# Accelerating Data Parallel Applications via Hardware and Software Techniques

by

#### Ramin Bashizade

Department of Computer Science Duke University

| Date:                    |

|--------------------------|

| Approved:                |

|                          |

|                          |

| Alvin R. Lebeck, Advisor |

|                          |

|                          |

| Sayan Mukherjee          |

|                          |

|                          |

| Daniel J. Sorin          |

|                          |

|                          |

| Hai Li                   |

|                          |

|                          |

| Lisa Wu Wills            |

#### **Abstract**

# Accelerating Data Parallel Applications via Hardware and Software Techniques

by

#### Ramin Bashizade

Department of Computer Science Duke University

| Date:                    |

|--------------------------|

| Approved:                |

|                          |

|                          |

|                          |

|                          |

| Alvin R. Lebeck, Advisor |

|                          |

|                          |

|                          |

| Sayan Mukherjee          |

| J J                      |

|                          |

|                          |

| Daniel J. Sorin          |

| Damer 9. Sorm            |

|                          |

|                          |

|                          |

| Hai Li                   |

|                          |

|                          |

|                          |

| Lisa Wu Wills            |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University 2020

Copyright © 2020 by Ramin Bashizade All rights reserved except the rights granted by the Creative Commons Attribution-Noncommercial Licence

### Abstract

The unprecedented amount of data available today opens the door to many new applications in areas such as finance, scientific simulation, machine learning, etc. Many such applications perform the same computations on different data, which are called data-parallel. However, processing this enormous amount of data is challenging, especially in the post-Moore's law era. Specialized accelerators are a promising solution to meet the performance requirements of data-parallel applications. Among these are graphics processing units (GPUs), as well as more application-specific solutions.

One of the areas with high performance requirements is statistical machine learning, which has widespread applications in various domains. These methods include probabilistic algorithms, such as Markov Chain Monte-Carlo (MCMC), which rely on generating random numbers from probability distributions. These algorithms are computationally expensive on conventional processors, yet their statistical properties, namely, interpretability and uncertainty quantification compared to deep learning, make them an attractive alternative approach. Therefore, hardware specialization can be adopted to address the shortcomings of conventional processors in running these applications.

In addition to hardware techniques, probabilistic algorithms can benefit from algorithmic optimizations that aim to avoid performing unnecessary work. To be more specific, we can skip a random variable (RV) whose probability distribution function (PDF) is concentrated on only one value, i.e., there is only one value to

choose, and the values of its neighboring RVs have not changed. In other words, if a RV has a concentrated PDF, its PDF will remain concentrated until at least one of its neighbors changes. Due to their high throughput and centralized scheduling mechanism, GPUs are a suitable target for this optimization.

Other than probabilistic algorithms, GPUs can be utilized to accelerate a variety of applications. GPUs with their Single-Instruction Multiple-Thread (SIMT) execution model offer massive parallelism that is combined with a relative ease of programming. The large amount and diversity of resources on the GPU is intended to ensure applications with different characteristics can achieve high performance, but at the same time it means that some of these resources will remain under-utilized, which is inefficient in a multi-tenant environment.

In this dissertation, we propose and evaluate solutions to the challenges mentioned above, namely i) accelerating probabilistic algorithms with uncertainty quantification, ii) optimizing probabilistic algorithms on GPUs to avoid unnecessary work, and iii) increasing resource utilization of GPUs in multi-tenant environments.

| To my fa of my mom. | y my best friei | nd and wife, N | Mohaddeseh, a | nd to the memo | ory |

|---------------------|-----------------|----------------|---------------|----------------|-----|

|                     |                 |                |               |                |     |

|                     |                 |                |               |                |     |

|                     |                 |                |               |                |     |

|                     |                 |                |               |                |     |

|                     |                 |                |               |                |     |

|                     |                 |                |               |                |     |

vi

# Contents

| A  | bstra | act                                                                              | iv                     |  |

|----|-------|----------------------------------------------------------------------------------|------------------------|--|

| Li | st of | Tables                                                                           | xi                     |  |

| Li | st of | Figures                                                                          | xii                    |  |

| A  | ckno  | wledgements                                                                      | $\mathbf{x}\mathbf{v}$ |  |

| 1  | Intr  | ntroduction                                                                      |                        |  |

|    | 1.1   | Accelerating Markov Random Field Inference with Uncertainty Quantification       | 3                      |  |

|    | 1.2   | Optimizing Markov Random Field Inference via Event-driven Gibbs Sampling on GPUs | 4                      |  |

|    | 1.3   | Adaptive Simultaneous Multi-tenancy for GPUs                                     | 4                      |  |

|    | 1.4   | Dissertation Outline                                                             | 5                      |  |

| 2  | Bac   | ackground                                                                        |                        |  |

|    | 2.1   | Markov Random Field                                                              | 6                      |  |

|    | 2.2   | Probabilistic Algorithms                                                         | 7                      |  |

|    | 2.3   | GPU Execution Model                                                              | 8                      |  |

| 3  |       | elerating Markov Random Field Inference with Uncertainty Qua                     | n-<br>10               |  |

|    | 3.1   | Motivation                                                                       | 12                     |  |

|    |       | 3.1.1 Example Application: Motion Estimation                                     | 12                     |  |

|    |       | 3.1.2 Uncertainty Quantification                                                 | 14                     |  |

|   | 3.2 | Design | 1 Overview and Challenges                                         | 15 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   | 3.3 | Stocha | astic Processing Accelerator                                      | 18 |

|   |     | 3.3.1  | Overview                                                          | 18 |

|   |     | 3.3.2  | Stochastic Processing Unit                                        | 19 |

|   |     | 3.3.3  | Stochastic Processing Element                                     | 21 |

|   |     | 3.3.4  | Accelerator Topology                                              | 30 |

|   |     | 3.3.5  | Runtime                                                           | 34 |

|   |     | 3.3.6  | Limitations and Future Work                                       | 34 |

|   | 3.4 | Metho  | odology                                                           | 35 |

|   |     | 3.4.1  | Applications and Metrics                                          | 35 |

|   |     | 3.4.2  | HLS Implementation                                                | 36 |

|   |     | 3.4.3  | GPU Implementation                                                | 37 |

|   | 3.5 | Evalua | ation                                                             | 37 |

|   |     | 3.5.1  | ASIC Analysis                                                     | 40 |

|   | 3.6 | Relate | ed Work                                                           | 42 |

|   | 3.7 | Summ   | ary                                                               | 44 |

| 4 | _   |        | g Markov Random Field Inference via Event-driven Gibbs<br>on GPUs | 46 |

|   | 4.1 | Motiva | ation                                                             | 47 |

|   |     | 4.1.1  | Approximation in Gibbs Sampling                                   | 47 |

|   |     | 4.1.2  | Stable Random Variables                                           | 48 |

|   | 4.2 | Event- | -Driven Gibbs Sampling                                            | 49 |

|   | 4.3 | EDGS   | Implementation for GPUs                                           | 52 |

|   | 4.4 | Evalua | ation                                                             | 54 |

|   |     | 4.4.1  | Methodology                                                       | 54 |

|   |     | 4.4.2  | Results                                                           | 58 |

|   |     | 4.4.3  | Takeaways                                 | 66  |

|---|-----|--------|-------------------------------------------|-----|

|   | 4.5 | Relate | ed Work                                   | 67  |

|   | 4.6 | Summ   | nary                                      | 68  |

| 5 | Ada | aptive | Simultaneous Multi-tenancy for GPUs       | 70  |

|   | 5.1 | Motiv  | ration                                    | 75  |

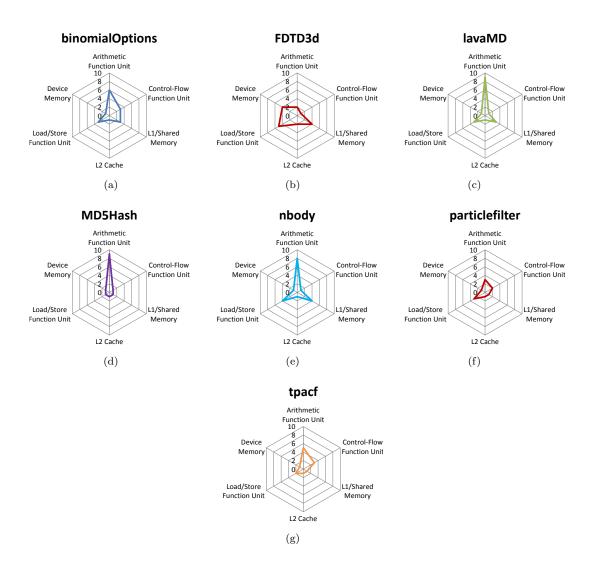

|   |     | 5.1.1  | Resource Requirements                     | 75  |

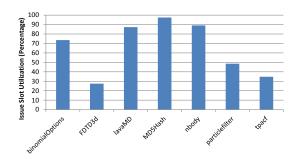

|   |     | 5.1.2  | Issue Slot Utilization                    | 76  |

|   |     | 5.1.3  | Non-overlapping Execution                 | 76  |

|   | 5.2 | Adapt  | tive Simultaneous Multi-tenancy           | 77  |

|   |     | 5.2.1  | Overview                                  | 77  |

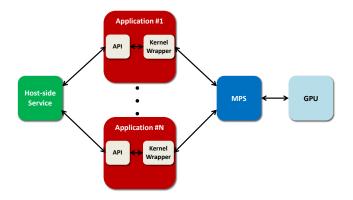

|   |     | 5.2.2  | Host-side Service                         | 79  |

|   |     | 5.2.3  | Application Side                          | 80  |

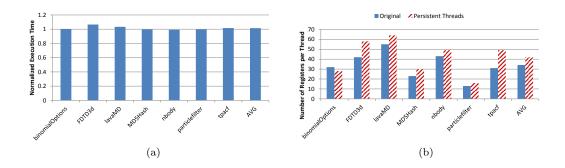

|   |     | 5.2.4  | Kernel Code Transformation                | 82  |

|   |     | 5.2.5  | Profiling and Pruning the Parameter Space | 85  |

|   |     | 5.2.6  | Sharing Policy                            | 86  |

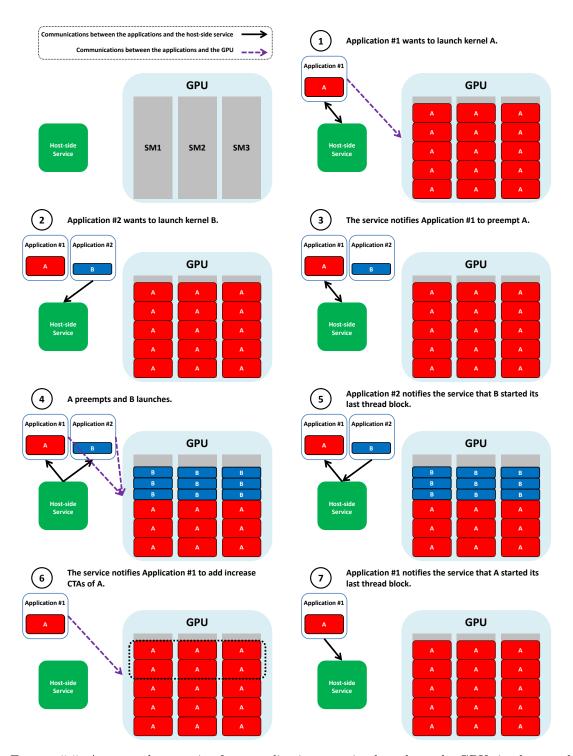

|   |     | 5.2.7  | Example Scenario                          | 87  |

|   |     | 5.2.8  | Limitations and Future Work               | 90  |

|   | 5.3 | Evalua | ation                                     | 91  |

|   |     | 5.3.1  | Platform                                  | 91  |

|   |     | 5.3.2  | Benchmark Kernels                         | 91  |

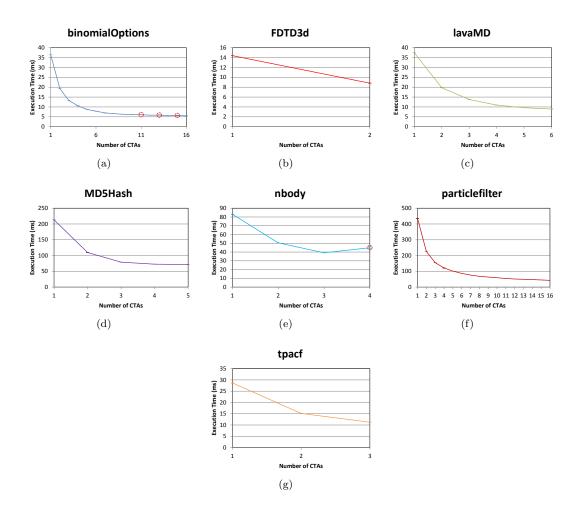

|   |     | 5.3.3  | Single Kernel Performance                 | 93  |

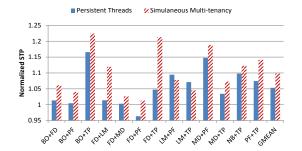

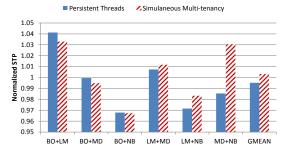

|   |     | 5.3.4  | Multi-Kernel Performance                  | 95  |

|   | 5.4 | Relate | ed Work                                   | 98  |

|   | 5.5 | Summ   | nary                                      | 100 |

| 6 | Cor | olucio | ne                                        | 102 |

| Bibliography | 106 |

|--------------|-----|

| Biography    | 116 |

# List of Tables

| 3.1 | Values used to calculate Equation 3.5 for Figure 3.8             | 29 |

|-----|------------------------------------------------------------------|----|

| 3.2 | Application parameters used in evaluations                       | 36 |

| 3.3 | FPGA prototypes results                                          | 38 |

| 3.4 | Qualitative comparison of proposed accelerator with related work | 43 |

| 4.1 | Parameters for design space exploration                          | 54 |

| 4.2 | Application parameters used in the evaluations                   | 57 |

| 4.3 | Best performing configurations for the baseline and EDGS         | 63 |

| 5.1 | Application API                                                  | 81 |

| 5.2 | NVIDIA Tesla K40c specifications                                 | 91 |

| 5.3 | Benchmark kernels characteristics.                               | 92 |

# List of Figures

| 2.1  | Markov Chain Monte Carlo algorithm for Markov Random Field              | (  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Streaming Multiprocessor (SM) components                                | ć  |

| 2.3  | GPU components                                                          | Ć  |

| 2.4  | Kernel structure                                                        | Ć  |

| 3.1  | Data access patterns for performing first-order MRF inference           | 13 |

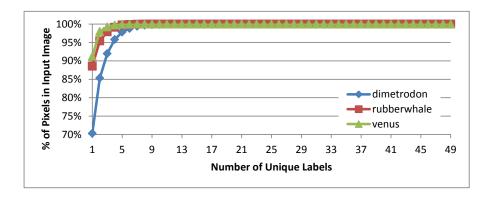

| 3.2  | Cumulative distribution of pixels per number of unique labels           | 14 |

| 3.3  | Overview of the proposed accelerator's architecture                     | 17 |

| 3.4  | SPU microarchitecture, reproduced from [105]                            | 20 |

| 3.5  | Architecture of an SPE with two SPUs                                    | 21 |

| 3.6  | Example singleton 2 access pattern and proposed baking scheme. $$ .     | 25 |

| 3.7  | Memory banking scheme for LMem                                          | 26 |

| 3.8  | Maximum per iteration bandwidth usage                                   | 28 |

| 3.9  | LMem entry and off-chip message bit structure                           | 30 |

| 3.10 | Estimated resources for links and crossbars in SPE topology             | 31 |

| 3.11 | Replicating singleton 2 data to eliminate long communication path. $$ . | 33 |

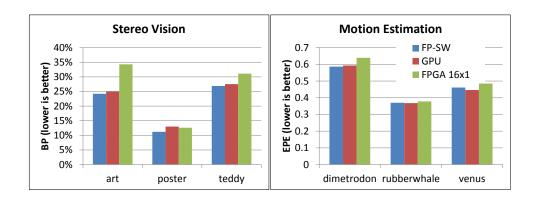

| 3.12 | Comparison of output quality results                                    | 38 |

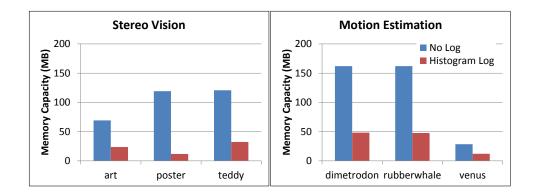

| 3.13 | Memory space to store data for generating labels histogram              | 39 |

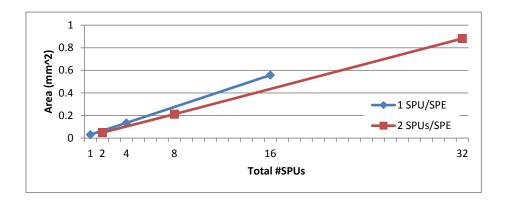

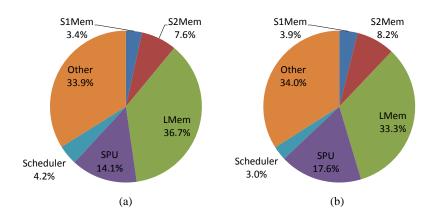

| 3.14 | Accelerator area at different design points                             | 40 |

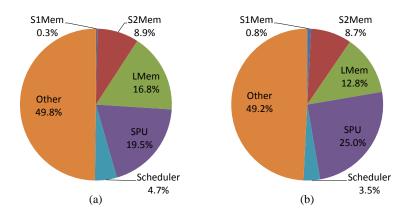

| 3.15 | SPE area breakdown with one and two SPU(s)                              | 41 |

| 3.16 | SPE power breakdown with one and two SPU(s)                             | 42 |

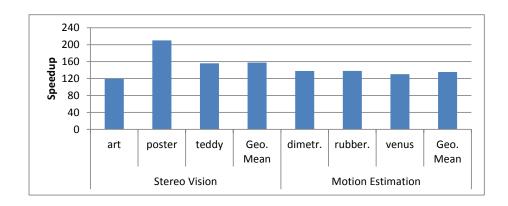

| 3.17 | Speedup of a 1024×2 SPE ASIC design compared to GPU                                                                 | 42 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

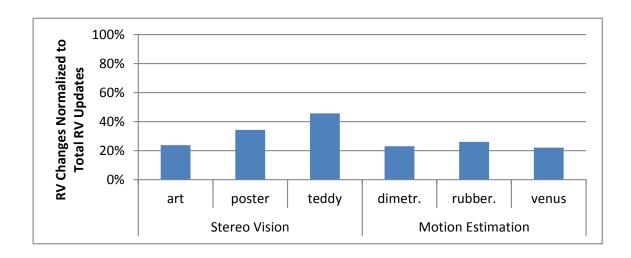

| 4.1  | Normalized number of label changes with respect to total updates                                                    | 48 |

| 4.2  | Comparison of update procedure in baseline and EDGS                                                                 | 50 |

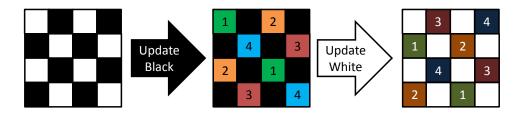

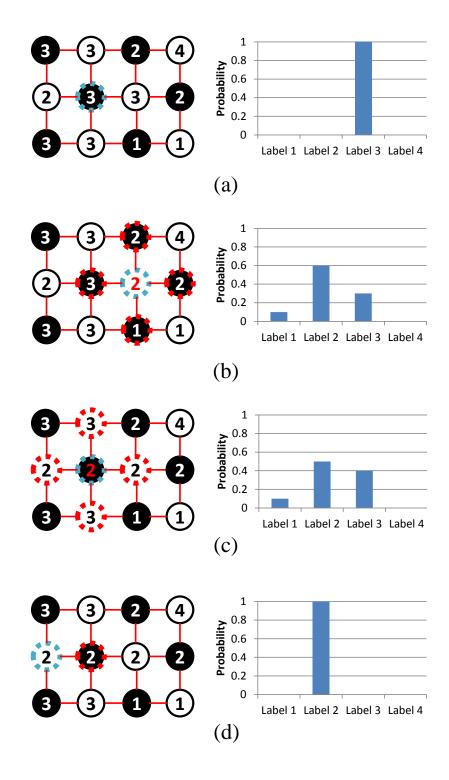

| 4.3  | An example scenario of updating RVs in a first-order MRF using EDGS.                                                | 51 |

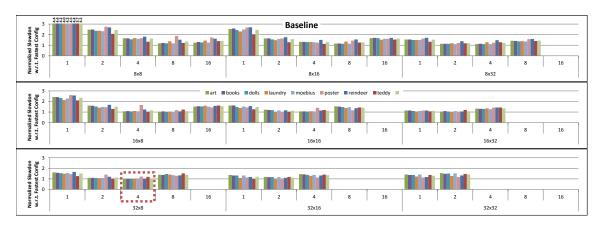

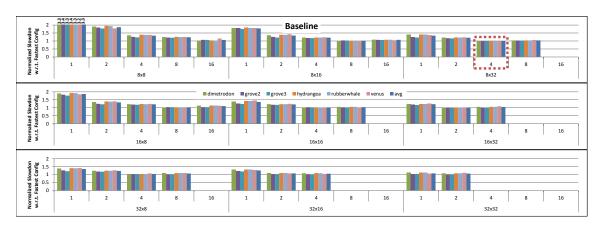

| 4.4  | Normalized slowdown of baseline design points for stereo vision                                                     | 55 |

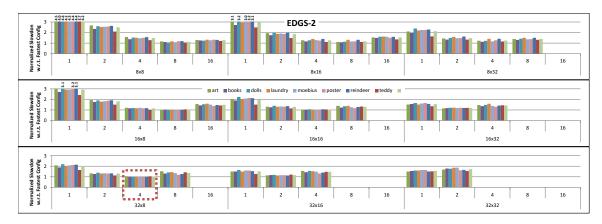

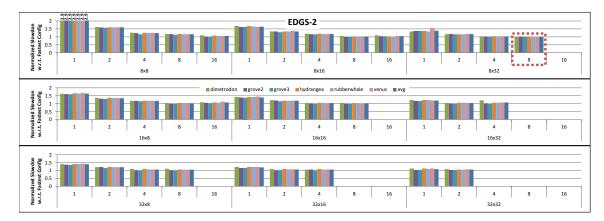

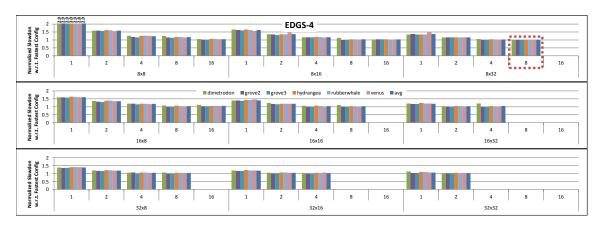

| 4.5  | Normalized slowdown of EDGS-2 design points for stereo vision                                                       | 55 |

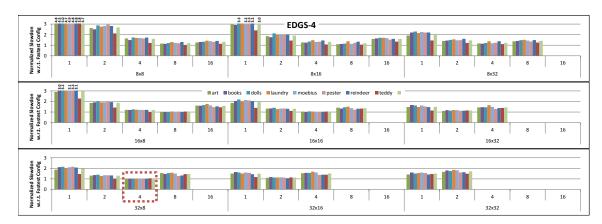

| 4.6  | Normalized slowdown of EDGS-4 design points for stereo vision                                                       | 56 |

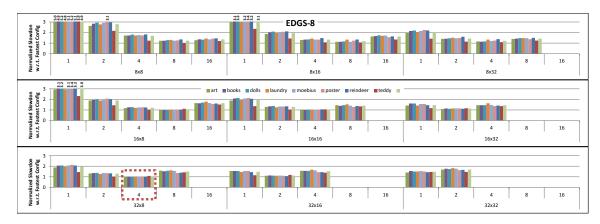

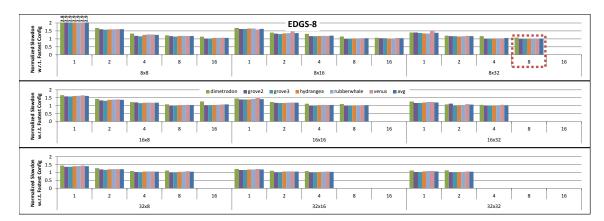

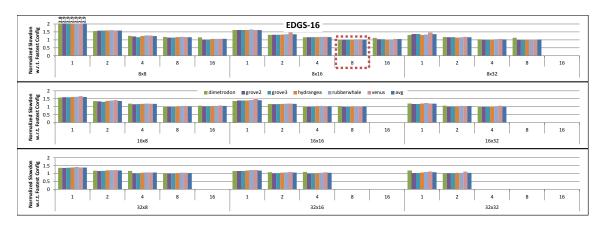

| 4.7  | Normalized slowdown of EDGS-8 design points for stereo vision                                                       | 56 |

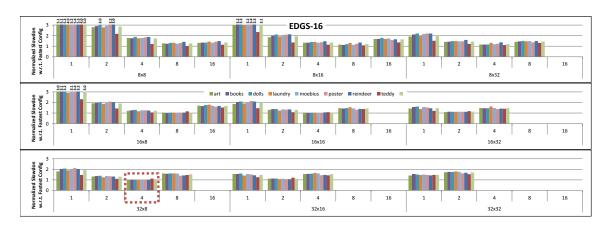

| 4.8  | Normalized slowdown of EDGS-16 design points for stere<br>o vision. $\ .$ .                                         | 57 |

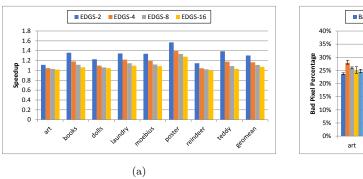

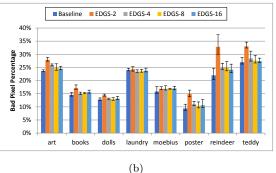

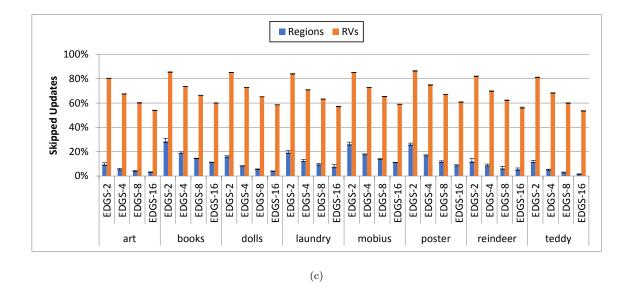

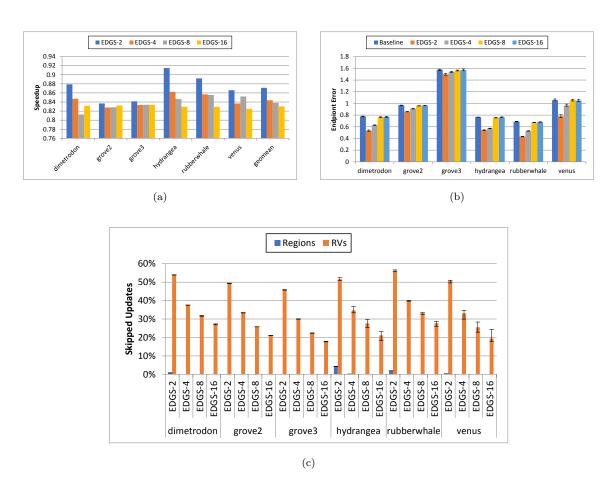

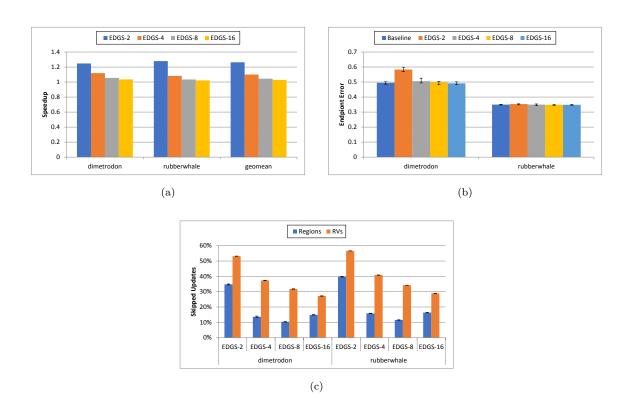

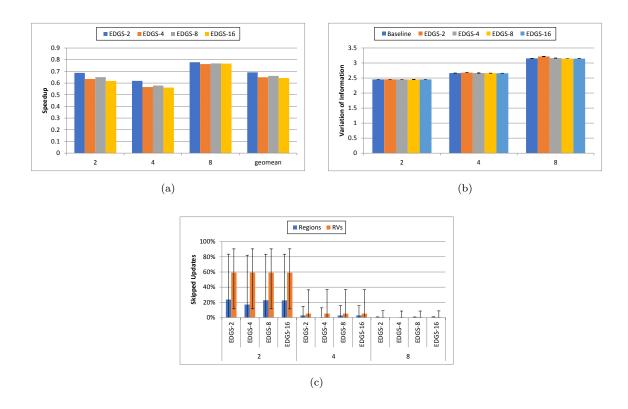

| 4.9  | Speedup, end-point error, and skipped update percentages of EDGS for stereo vision                                  | 59 |

| 4.10 | Normalized slowdown of baseline design points for motion estimation.                                                | 60 |

| 4.11 | Normalized slowdown of EDGS-2 design points for motion estimation.                                                  | 60 |

| 4.12 | Normalized slowdown of EDGS-4 design points for motion estimation.                                                  | 61 |

| 4.13 | Normalized slowdown of EDGS-8 design points for motion estimation.                                                  | 61 |

| 4.14 | Normalized slowdown of EDGS-16 design points for motion estimation.                                                 | 62 |

| 4.15 | Speedup, end-point error, and skipped update percentages of EDGS for motion estimation with a $15 \times 15$ window | 62 |

| 4.16 | Speedup, end-point error, and skipped update percentages of EDGS for motion estimation with a $7\times7$ window     | 63 |

| 4.17 | Speedup, end-point error, and skipped update percentages of EDGS for image segmentation                             | 65 |

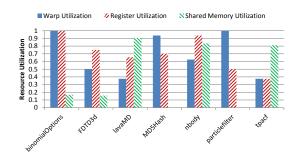

| 5.1  | Spatial utilization of different resource types in SMs for the benchmark kernels                                    | 75 |

| 5.2  | Issue slot utilization for the benchmark kernels                                                                    | 75 |

| 5.3  | Overview of the proposed adaptive simultaneous multi-tenant system.                                                 | 78 |

| 5.4  | The kernel transformation for persistent threads and preemption                                                     | 83 |

| 5.5  | simultaneously                                                              | 88 |

|------|-----------------------------------------------------------------------------|----|

| 5.6  | Utilization of various resource types in benchmark kernels                  | 93 |

| 5.7  | Performance and register usage of benchmark kernels                         | 94 |

| 5.8  | Performance of benchmark kernels with different numbers of CTAs             | 95 |

| 5.9  | Normalized STP for combinations of kernels with at least one low-ISU kernel | 96 |

| 5.10 | Normalized STP for combinations of kernels with high-ISU kernels            | 96 |

### Acknowledgements

I would like to express my sincere gratitude to all the people without whom I would not have been able to complete my Ph.D. studies. My advisor, Professor Alvin R. Lebeck, supported and patiently guided me even when I was disappointed in myself. I am grateful to Professor Sayan Mukherjee who helped me in my research in probabilistic computing. I also thank my other committee members, Professors Daniel J. Sorin, Hai Li, and Lisa Wu Wills; and other current and former faculty members at Duke Computer Science Department from whom I learned a lot, Professors Benjamin C. Lee, Andrew Hilton, Jeffrey Chase, Landon Cox, and many others. I also appreciate the financial support from Duke University, National Science Foundation, and Intel Corporation.

Past and present staff members at the Duke Computer Science Department were so kind they made everything seem so simple. Pam Spencer, Melanie Eberhart, Alison Hriciga, and most importantly, Marilyn Butler, who always went out of her way to help me in all matters, academic and non-academic alike. Joe Shamblin, and all IT Lab staff in general, helped me a lot with servers and equipment.

I am also thankful to my friends and collaborators at Duke University. Especially Xiangyu Zhang, who was very kind and always willing to help, and Pulkit Misra, a great office-mate and a fellow soccer fan, and others in the Computer Sceince Department.

Finally, I would like to deeply thank my best friend and wife, Mohaddeseh, who

always supported me through the difficult times. I hope I can return her favor in the many years we will have together.

1

### Introduction

Today there is more data available than ever before. This unprecedented amount of data opens the door to many new applications in areas such as finance [26], scientific simulation [28], machine learning [57], etc. Many such applications perform the same computations on different data, which are called data-parallel. However, processing this enormous amount of data is challenging, especially in the post-Moore's law era [92]. As a result, to address the shortcomings of general-purpose processors in meeting the performance requirements of data-parallel applications, architects have turned to specialized accelerators. Among these are graphics processing units (GPUs), as well as more application-specific solutions.

One of the areas with high performance requirements is statistical machine learning, which has widespread applications in various domains [5, 12, 27, 37, 38, 54, 63, 64, 88]. These methods include probabilistic algorithms, such as Markov Chain Monte-Carlo (MCMC), which rely on generating random numbers from probability distributions. These algorithms are computationally expensive on conventional processors, yet their statistical properties, namely, interpretability and uncertainty quantification compared to deep learning, make them an attractive alternative approach.

Therefore, hardware specialization can be adopted to address the shortcomings of conventional processors in running these applications.

In addition to hardware techniques, probabilistic algorithms can benefit from algorithmic optimizations that aim to avoid performing unnecessary work. These algorithms operate in two modes, sampling and optimization, which provide either the distribution of the result (sampling) or more quickly converge to the final result (optimization). In the optimization mode, most Random Variables (RVs) tend to not change labels very often, and the adoption of approximation techniques makes this more likely to happen. Therefore, we can detect this scenario and further speedup the application by skipping the computations for those RVs. To be more specific, we can skip a random variable (RV) whose probability distribution function (PDF) is concentrated on only one value, i.e., there is only one value to choose, and the values of its neighboring RVs have not changed. In other words, if a RV has a concentrated PDF, its PDF will remain concentrated until at least one of its neighbors changes. Due to their high throughput and centralized scheduling mechanism, GPUs are a suitable target for this optimization.

Other than probabilistic algorithms, GPUs can be utilized to accelerate a variety of applications. GPUs with their Single-Instruction Multiple-Thread (SIMT) execution model offer massive parallelism that is combined with relative ease of programming. They provide thousands of simple cores, register files, and a memory system that is designed to hide latency with high throughput achieved by executing many threads concurrently. The large amount and diversity of resources on the GPU is intended to ensure applications with different characteristics can achieve high performance, but at the same time it means that some of these resources will remain under-utilized. Moreover, the trend in moving toward cloud computing and multitenant environments where infrastructure is shared among multiple applications amplifies the inefficiency of leaving resources under-utilized, and further highlights the

importance of better resource utilization.

In the remainder of this chapter, we briefly introduce our proposed solutions to the challenges mentioned above, namely i) accelerating probabilistic algorithms with uncertainty quantification, ii) optimizing probabilistic algorithms on GPUs to avoid unnecessary work, and iii) increasing resource utilization of GPUs in multi-tenant environments.

#### 1.1 Accelerating Markov Random Field Inference with Uncertainty Quantification

A Markov Random Field (MRF) is a powerful graphical model for representing a wide range of applications in statistical machine learning. A MRF encodes the conditional dependence among random variables (RVs). One approach to solving problems represented by a MRF is using probabilistic algorithms such as Gibbs sampling. These methods go through all RVs in the MRF and update them iteratively.

We propose a high-throughput accelerator for MRF inference using Gibbs sampling. We design a tiled architecture that takes advantage of near-memory computing and memory banking and communication schemes tailored to the semantics of MRF. Additionally, we propose a hybrid on-chip/off-chip memory system to efficiently support uncertainty quantification. We implement an FPGA prototype of our proposed architecture using high-level synthesis tools and achieve 146MHz frequency for an accelerator with 32 function units on an Intel Arria 10 FPGA. Compared to prior work on FPGA, our accelerator achieves 26× speedup. ASIC analysis in 15nm technology node shows that our design with 2048 function units running at 3GHz outperforms GPU implementations of motion estimation and stereo vision run on Nvidia RTX 2080 Ti by 135× and 158×, respectively, while occupying only 7.7% of the area.

# 1.2 Optimizing Markov Random Field Inference via Event-driven Gibbs Sampling on GPUs

Probabilistic algorithms such as Gibbs sampling operate in two modes of sampling and optimization, which provide either the distribution of the result (sampling) or more quickly converge to the final result (optimization). We build on three observations in the optimization mode to skip updating RVs that cannot change their label during the current iteration, hence avoiding unnecessary work: i) after the warm-up period, most RVs tend to not change labels very often, ii) an RV can only change its label if either it has a non-concentrated probability distribution function (PDF), or at least one of the RVs on which it is conditionally dependent has changed its label, and iii) approximation techniques make it increasingly likely that RVs have concentrated PDFs. Therefore, we introduce Event-Driven Gibbs Sampling (EDGS), which only updates RVs when necessary. Our analysis shows that 26.3%-30.3% speedup can be gained for two applications, motion estimation and stereo vision on a GPU compared to a baseline that does not take advantage of EDGS. However, for image segmentation, the overheads of our approach are higher than its benefits. In addition, our observations show that in the case of an application with a large number of labels, the approximation technique used actually increases the output quality.

#### 1.3 Adaptive Simultaneous Multi-tenancy for GPUs

GPUs are energy-efficient, massively parallel accelerators that are increasingly deployed in multi-tenant environments such as datacenters for general-purpose computing as well as graphics applications. Using GPUs in multi-tenant setups requires an efficient and low-overhead method for sharing the device among multiple users that improves system throughput while adapting to the changes in workload. This requires mechanisms to control the resources allocated to each kernel, and an efficient policy to make decisions about this allocation.

We propose adaptive simultaneous multi-tenancy to address these issues. Adaptive simultaneous multi-tenancy allows for sharing the GPU among multiple kernels, as opposed to single kernel multi-tenancy that only runs one kernel on the GPU at any given time and static simultaneous multi-tenancy that does not adapt to events in the system. Our proposed system dynamically adjusts the kernels' parameters at run-time when a new kernel arrives or a running kernel ends. Evaluations using our prototype implementation show that, compared to sequentially executing kernels, the system throughput is improved by an average of 9.8% (and up to 22.4%) for combinations of kernels that include at least one low-utilization kernel.

#### 1.4 Dissertation Outline

The rest of this dissertation is organized as follows. Chapter 2 presents the necessary background on probabilistic algorithms and GPUs. Chapter 3 describes the design of our proposed accelerator for MRF inference with Gibbs sampling, which supports uncertainty quantification, along with the evaluation results on an FPGA prototype and ASIC analysis. The proposed optimization for Gibbs sampling which detects stable RVs and skips updating them is explained in Chapter 4. We implement and evaluate this optimization on a GPU, but we also discuss the limitations of the GPU execution model and provide results that demonstrate the full potential of our proposed approach. In Chapter 5, we present and evaluate our multi-tenant system for GPUs, in addition to the analysis of the effectiveness of the system under various workload scenarios. Finally, the conclusion and future directions are discussed in Chapter 6.

### Background

In this chapter, we first briefly explain MRF and probabilistic algorithms (Sections 2.1 and 2.2, respectively), and then present the background on GPU execution model (Section 2.3).

#### 2.1 Markov Random Field

A Markov Random Field (MRF) is an undirected graphical model for representing the dependencies among a set of RVs, which satisfies the Markov property, i.e., the future state of the process only depends on the current state and not any previous

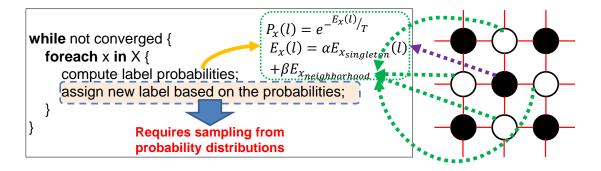

FIGURE 2.1: Markov Chain Monte Carlo algorithm (left) for Markov Random Field (right) inference. Note that sampling is performed in the inner loop.

states. A MRF can be used to represent a wide range of applications in statistical machine learning. In this dissertation, we address problems that are represented by a first-order MRF, but we expect most of the techniques to be applicable to other types of MRF too, albeit after undergoing some modifications.

Figure 2.1 (right) illustrates an example first-order MRF model and its connection with the Gibbs sampling algorithm. In the model, each RV depends on its four immediate neighbors. Due to this structure, the first-order MRF model can be divided into two regions so that all RVs in each region are conditionally independent. This enables us to generate a chromatic schedule to update all RVs in each region in parallel [29, 31, 46, 91].

#### 2.2 Probabilistic Algorithms

Bayesian inference combines new evidence and prior beliefs to update the probability estimate for a hypothesis. Consider D as the observed data and X as the latent random variable. The prior distribution of X is p(X) and  $p(D \mid X)$  is the probability of observing D given a certain value of X. In Bayesian inference, the goal is to retrieve the posterior distribution  $p(X \mid D)$  of the random variable X when D is observed. As the dimensions of D and X increase, it often becomes difficult or intractable to numerically derive the exact posterior distribution  $p(X \mid D)$ .

One approach to solving these inference problems is to use probabilistic Markov chain Monte-Carlo (MCMC) methods, e.g., Gibbs sampling [29], that converge to an exact solution by iteratively generating samples for RVs. Figure 2.1 shows this process. For each label l of RV x, we calculate an energy value using the singleton data and neighbor labels  $(E_x(l))$ . Singleton and neighborhood energies are weighted by parameters  $\alpha$  and  $\beta$ , which are application-specific. Having  $E_x(l)$ , a probability  $P_x(l)$  is computed for each label using  $exp(-E_s(l)/T)$ , in which T is a per iteration parameter. Once all label probabilities are calculated, we sample from the cumulative

distribution function (CDF) by generating a uniform random number and seeing where it falls in the range of the CDF. The result is the new label for RV x in the current iteration.

Gibbs sampling may be used in one of two modes: i) pure sampling, or ii) optimization. The main difference between these two modes is that in pure sampling, the parameter T is the same for all Gibbs sampling iterations, whereas in optimization (simulated annealing), T gradually decreases to help faster convergence to the final solution. A more detailed explanation of Gibbs sampling is provided elsewhere [29].

In practice, MCMC becomes inefficient for many problems that have high dimensionality (i.e., many RVs) and complex structure. It can require many iterations before convergence, and the inner loop in Figure 2.1 includes generating samples from probability distributions, which is computationally expensive for conventional processors [95]. Therefore, massively parallel platforms such as GPUs can be utilized to address these shortcomings.

#### 2.3 GPU Execution Model

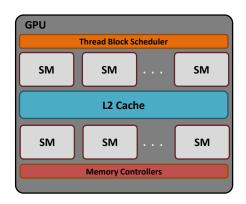

GPUs are massively parallel accelerators that are composed of thousands of simple cores. A large number of cores together with cache, shared memory, <sup>1</sup> register files, and some other components form streaming multi-processors (SMs). All SMs share a last level cache. Figures 2.2 and 2.3 show the architecture of an SM and the GPU.

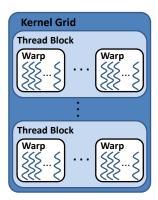

Figure 2.4 illustrates the structure of a kernel. GPU kernels comprise a large number of threads that execute the same instructions on different data, hence the name Single-Instruction-Multiple-Thread (SIMT). These threads are grouped together to form thread blocks, and a set of thread blocks is called a grid. All thread blocks in a grid have the same dimensions, and all threads of the same thread block can only run on a single SM. A thread block is a logical notion that helps the programmers

$<sup>^{1}</sup>$  Scratchpad memory in NVIDIA terminology is called shared memory.

FIGURE 2.2: Streaming Multiprocessor (SM) components.

FIGURE 2.3: GPU components.

FIGURE 2.4: Kernel structure.

reason about their code. However, a limited number of thread blocks can fit on the device at the same time. We separate these concepts and refer to the physical thread blocks actually running on the GPU as concurrent thread arrays (CTAs). Note that in some other works thread blocks and CTAs are used interchangeably.

When there are enough resources on an SM to host a waiting thread block, the block scheduler dispatches that thread block to the available SM for execution. If there are more than one SM with enough resources, the mapping happens in a round-robin fashion. In each SM then, the warp scheduler dispatches ready warps to execute instructions. A warp is the smallest group of threads that execute in lockstep to reduce the overhead of instruction fetch and control flow. The programmer has no control over the size of a warp. Once a thread block is mapped to an SM, it continues execution until it finishes. In other words, there is no mechanism for preemption or yielding resources (the Pascal [68] and Volta [70] architectures perform context switching, but the programmer does not have control over the operation).

## Accelerating Markov Random Field Inference with Uncertainty Quantification

Compared to Deep Neural Networks, probabilistic algorithms make it easier to gain insight into why a result is obtained, and to what degree we can be certain about the results. This can be achieved by quantifying the uncertainty of the result, which is a valuable property of probabilistic algorithms, such as MCMC, and is of utmost importance for some applications, such as many image segmentation applications where quantifying the uncertainty in the segmentation boundaries is crucial (e.g., a surgeon's decision to resect what sections of a tumor will be impacted by the segmentation generated by an algorithm [16, 60]).

However, the benefits of MCMC come at a price. Since MCMC requires iteratively sampling from probability distributions, it is often computationally intensive. This is due to the significant overhead of sampling in conventional processors [95]. Furthermore, MCMC at first appears to be a sequential algorithm because updating each random variable (RV) depends on the latest value of all other RVs, which means that it may take a long time to finish. Deploying pseudo-random number

generation can help reduce the sampling inefficiency [105]. To avoid the overhead of serial execution, though, one can take advantage of the conditional independence of RVs, i.e., develop a schedule which allows multiple independent RVs to be updated in parallel [29, 31, 46, 91].

In this chapter, we propose an accelerator which builds on these ideas and fuses them with architectural contributions that allow fast and efficient execution of MCMC and minimize the overhead of uncertainty quantification. To be more specific, we propose a tiled architecture to exploit near-memory computing, and the parallelism exposed by taking advantage of the conditional independence of RVs in the first-order Markov Random Field model. We develop memory banking and on-chip communication schemes tailored to the semantics of the model to facilitate a stall-free pipeline.

In addition to the tiled architecture for the accelerator, we propose a hybrid onchip/off-chip memory system to support uncertainty quantification by maintaining a log of the values that RVs take on, called their labels, throughout the MCMC execution. By carefully analyzing the behavior of two image analysis applications [9, 53], we observe that most RVs take on a limited number of unique labels during the execution, and thus, we design this memory system such that it strikes a balance between on-chip memory capacity and off-chip communication bandwidth.

We implemented an FPGA prototype of our proposed design using Intel High-Level Synthesis (HLS) compiler [40], and developed the necessary runtime to verify and evaluate our implementation using real-world applications and input datasets. The results show that our design achieves a clock rate of 146MHz and a throughput of 4.672B labels/sec on an Arria 10 FPGA. This is a 26× speedup over the previous work [51]. We also perform ASIC analysis on our HLS implementation using Mentor Graphics HLS Compiler [33] and show that an accelerator with 2048 function units running at 3GHz in 15nm technology node [65] outperforms GPU implementations

of motion estimation and stereo vision on an RTX 2080 Ti by  $135 \times$  and  $158 \times$ , respectively.

#### 3.1 Motivation

One approach to solving inference problems is to use probabilistic Markov chain Monte-Carlo (MCMC) methods that converge to an exact solution by iteratively generating samples for RVs (Figure 2.1). In practice, MCMC becomes inefficient for many problems that have high dimensionality and complex structure. It can require many iterations before convergence, and the inner loop in Figure 2.1 includes generating samples from probability distributions, which is computationally expensive for conventional processors [95] and thus, a specialized accelerator is needed to address these shortcomings.

#### 3.1.1 Example Application: Motion Estimation

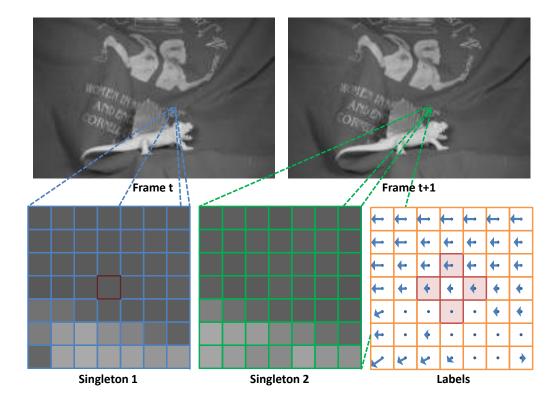

To shed more light on the details of the first-order MRF inference using MCMC algorithm, we explain how first-order MRF can be utilized to represent the motion estimation problem and how MCMC with Gibbs sampling can solve it [53]. The goal is to estimate the 2-D motion vectors between two time-varying images, such as two consecutive frames of a video. Figure 3.1 (top) shows a sample input for this problem.

In this example, the target is to compute the motion vector of the pixel in the center of the blue box in Figure 3.1 (bottom-left). To do so, the inner loop in Figure 2.1 must be executed, which includes computing the probability values according to the equations in the figure. In the equations,  $P_x(l)$  is the probability that RV x takes on label l,  $E_x(l)$  is the energy of label l which depends on the singleton and neighborhood values, and  $\alpha$ ,  $\beta$ , and T are application parameters.  $E_{x_{singleton}}$  depends on two types of singleton data: i) singleton 1, which is the gray-scale value of the pixel

FIGURE 3.1: Data access patterns for performing first-order MRF inference using MCMC to solve motion estimation (*dimetrodon* from Middlebury database [6]).

itself, and ii) singleton 2, which is the gray-scale value of each of the pixels inside the green box in Figure 3.1 (bottom-middle), which form a  $7 \times 7$  window surrounding the aforementioned pixel corresponding to possible labels (in this application, each motion vector) and come from frame t+1. The pattern of singleton 2 is application specific. Generally, for each RV,  $E_{x_{neighborhood}}$  may depend on the latest labels of all other RVs. However, for the first-order MRF model,  $E_{x_{neighborhood}}$  is calculated using the current labels of the top, down, left, and right neighbors of the pixel, the shaded boxes shown in Figure 3.1 (bottom-right), each of which are motion vectors themselves. This neighborhood pattern is fixed for the first-order MRF model. Once the probabilities for all possible labels are calculated, they are used to create a probability distribution function (PDF), which in turn is used for sampling and determining the new label for the pixel.

FIGURE 3.2: Cumulative distribution of pixels per number of unique labels in three input datasets [6] for motion estimation.

This process must be repeated for all pixels in frame t for a certain number of iterations (until the algorithm converges to the final solution) to obtain their motion vectors. CMOS specialization and pseudo-random number generation can be used to accelerate the computations required for updating each pixel. Previous work proposes a function unit for this purpose [105], which is briefly reviewed in Section 3.3.2. Furthermore, the structure of the MRF model provides opportunities for parallelism (explained in Section 3.3.3). However, there are challenges in realizing this parallelism due to the memory access patterns which require careful memory banking and access scheduling that are discussed in Sections 3.3.3 and 3.3.3.

#### 3.1.2 Uncertainty Quantification

Probabilistic models and algorithms are "conceptually simple, compositional, and interpretable" [30], and provide the opportunity to determine why a given result is obtained. This is due to two reasons: i) models such as MRF inherently have transparent structures, and ii) these algorithms allow for quantifying the uncertainty to evaluate the confidence in the obtained result. Uncertainty quantification can be achieved by collecting a histogram of the RV's labels after the warm-up period of the MCMC (i.e., the iterations at the beginning of the algorithm before mixing has

happened), which can then be used to derive statistics such as mode, variance, etc., that illuminate the uncertainty associated with the final result. In the example of image segmentation guiding a surgeon's decision regarding tumor resection, if the variance in the final result is high, then the surgeon might decide to remove a larger section to be safe, without removing too much of the tissue.

However, naïvely storing these data imposes a significant memory capacity, bandwidth, and processing overhead and therefore, a more scalable solution is required for uncertainty quantification. Fortunately, there is an opportunity for optimization because after warm-up, the RVs tend to take on only a limited number of labels. Figure 3.2 illustrates this fact. In three input datasets [6] for motion estimation, which has 49 labels, at most only 14.7% of pixels take on more than two unique labels during the second half of the iterations (i.e., iterations 1500-3000 in this experiment). This allows for having a limited on-chip memory space to store more frequently picked labels, and occasionally send the rest to the off-chip memory. Section 3.3.3 presents a hybrid on-chip/off-chip memory system for collecting the histogram of labels based on this analysis.

#### 3.2 Design Overview and Challenges

The characteristics of MCMC and MRF, covered in Sections 2.2 and 3.1.1, guide our design choices for the proposed accelerator. In this section, we provide an overview of our design, the challenges we face, and our proposed solutions.

MCMC is an iterative algorithm in which the computations of each iteration depend on those of the previous one (Section 2.2). Therefore, we decide to use on-chip memory to store data and intermediate iteration results to avoid frequent costly off-chip communication that uses up significant bandwidth and imposes high latencies. Furthermore, due to the structure of the first-oder MRF, all computations are local, i.e., updating RVs only needs data from nearby memory locations. *Thus, we propose*

to use a tiled architecture where each tile has its own memory and is responsible for computations on the portion of the graphical model stored in its memory. This allows us to expose the existing parallelism in first-order MRF and take advantage of nearmemory computing, and eliminates the need for complex centralized coordination. The tile's architecture is discussed in detail in Section 3.3.3.

The proposed architecture needs a communication infrastructure to efficiently transfer data among tiles when needed. Particularly, due to singleton 2's application-specific nature, designing such a communication infrastructure for it without sacrificing flexibility can be challenging. We propose a topology and data mapping scheme tailored to the first-order MRF characteristics, which together ensure no communication longer than one hop will be required, and therefore, the overheads of a full-blown Network-on-Chip (NoC) are avoided. Although our design is tailored to the first-order MRF neighborhood structure, it supports arbitrary accesses to the singleton 2 memory (S2Mem). In other words, our proposed topology and data mapping scheme for singleton 2 do not limit the MRF applications the accelerator can run. Sections 3.3.4 and 3.3.5 explain the proposed network topology and data mapping schemes. Different types of data are involved in the computations of the MRF model (i.e., read-only singletons and read-write labels) and unique access patterns to these data. Thus, we dedicate separate memories to each data type.

Moreover, exposing the potential parallelism inherent in the model requires a suitable scheduling technique that allows updating multiple conditionally independent RVs simultaneously. We use known techniques to develop a chromatic schedule of conditionally independent RVs that can be updated in parallel. The implication of this scheduling technique is that in addition to the parallelism between tiles, we can include more than one function unit in each tile to exploit intra-tile parallelism. However, this introduces competing accesses to S2Mem. Furthermore, labels memory (LMem) must be accessed at four different locations for each RV. Therefore, we

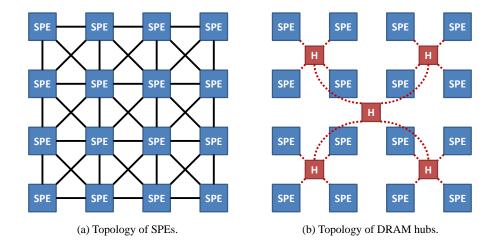

FIGURE 3.3: Overview of the proposed accelerator's architecture. Communication between SPEs is bi-directional, but between SPEs and DRAM hubs and among DRAM hubs is uni-directional. The diagonal links between SPEs are only for communicating singleton 2 data, whereas the vertical and horizontal links transfer both label data and singleton 2 data.

utilize memory banking mechanisms for each of S2Mem (Section 3.3.3) and LMem (Section 3.3.3) to facilitate stall-free execution in tiles.

Finally, to support uncertainty quantification, we need to track how many times a label is chosen for a given RV. A naïve implementation requires either i) having enough counters on the chip to keep track of all possible labels for all RVs, which is prohibitive in terms of area, or ii) sending the result of all label updates off chip, which needs significant communication bandwidth. Because of the limited memory capacity on the chip, and inspired by the insights from Figure 3.2, we design a hybrid on-chip/off-chip memory system to store the histogram for RVs during the MCMC iterations in the form of a log, which will be helpful for uncertainty quantification. We augment LMem entries with counters that keep track of how many times each label has been picked, and only transfer this information to off-chip memory when necessary (Section 3.3.3).

#### 3.3 Stochastic Processing Accelerator

#### 3.3.1 Overview

Our proposed architecture for accelerating first-order MRF inference using MCMC with Gibbs sampling is presented in this section. Figure 3.3 shows an overview of the accelerator's architecture. It is composed of a number of computation tiles or SPEs (Section 3.3.3), and DRAM hubs that route communication to the offchip DRAM. Each SPE is responsible for processing a portion of the input to take advantage of near-memory computing and exploit the inherent parallelism of the model. It comprises a number of Stochastic Processing Units (SPUs) [105], which perform the main MCMC computations (Section 3.3.2), in addition to a scheduler which sequences through RVs (Section 3.3.3), a portion of the singleton memories (Section 3.3.3) and the label memory (Section 3.3.3), on which it performs the MCMC updates, and communication components that transfer data between different SPEs and between the accelerator and the off-chip DRAM that stores the histogram log of the labels. Each SPE is connected to all its nearest SPEs and only communicates with those (Section 3.3.4). To ensure that communications longer than one hop are never required, appropriate data mapping and replication schemes are adopted, which are handled by the runtime (Section 3.3.5).

Figure 3.3 shows an overview of the proposed accelerator's architecture. It is composed of a number of computation tiles or Stochastic Processing Elements (SPEs), and DRAM hubs that route label histogram entries to the off-chip DRAM. Each SPE is responsible for processing a portion of the input to take advantage of near-memory computing and exploit the inherent parallelism of the model. It comprises a number of Stochastic Processing Units (SPUs), which perform the main MCMC computations (Section 3.3.2), in addition to a scheduler which sequences through RVs (Section 3.3.3), a portion of the singleton memories (Section 3.3.3) and the label

memory (Section 3.3.3), on which it performs the MCMC updates, and communication components that transfer data between different SPEs and between the accelerator and the off-chip DRAM that stores the histogram log of the labels. Each SPE is connected to all its nearest SPEs and only communicates with those SPEs (Section 3.3.4). To ensure that communications with SPEs more than one hop away are never required, appropriate data mapping and data replication schemes are adopted which are handled by the runtime (Section 3.3.5).

#### 3.3.2 Stochastic Processing Unit

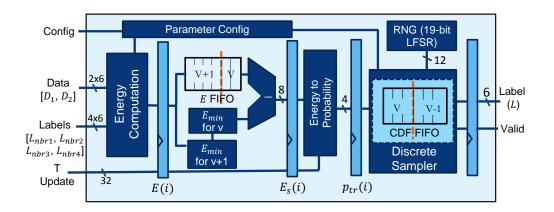

Zhang et al. propose a Gibbs sampling function unit, called Stochastic Processing Unit (SPU), that utilizes specialization and pseudo-random number generation to accelerate MCMC computations [105]. Figure 3.4 demonstrates the microarchitecture of this function unit. It is composed of four main pipeline stages, namely, energy computation (Equation 3.1), dynamic energy scaling (Equation 3.2), energy to probability conversion (Equations 3.3 and 3.4), and sampling.

$$E(l) = \alpha E_{singleton}(l) + \beta \sum E_{neighborhood}$$

(3.1)

$$E_s(l) = E(l) - E_{min} \tag{3.2}$$

$$P_s(l) = (2^{P_{bits}} - 1) \times exp(-E_s(l)/T)$$

(3.3)

$$P_{tr}(l) = \lfloor 2^{\lfloor \log_2 P_s(l) \rfloor} \rfloor \tag{3.4}$$

Energy computation takes the singleton data and neighbor labels, all 6-bit values, and computes the energy of a possible label, E(l) in Equation 3.1, where  $\alpha$  and  $\beta$  are application parameters. Next, E(l) is dynamically scaled by subtracting the minimum energy of all labels from it to maximize the dynamic range. Energy values (raw and scaled) are 8-bit unsigned integers. The scaled energy  $E_s(l)$  is then converted

FIGURE 3.4: SPU microarchitecture, reproduced from [105].

to a scaled probability represented by a 4-bit unsigned integer. The original probability (real number in [0,1]) is calculated using  $\exp(-E_s(l)/T)$ , in which T is a per iteration parameter. To avoid using floating-point function units, though, the probability is scaled using Equation 3.3, and then truncated using Equation 3.4.  $P_{bits} = 4$  ensures the scaled probability is in [0,16], which allows for representing the number using 4 bits. Afterward, Equation 3.4 approximates the scaled probabilities to the nearest power of two., i.e.,  $P_{tr} \in \{0,1,2,4,8\}$ . The possible values of  $P_{tr}(l)$  can be pre-computed and stored in a look-up table (LUT). These values must be updated if T changes. The last stage generates a sample per RV based on all  $P_{tr}(l)$ , where L is the number of labels, using the least significant twelve bits of a 19-bit Linear Feedback Shift Register (LFSR) to implement the inverse transform sampling. The SPU's throughput is one RV update per L cycles, if it receives the appropriate input (i.e., neighborhood labels and singleton data) at every cycle. Our goal in Sections 3.3.3 and 3.3.4 is to design an architecture that ensures this condition is realized.

The SPU can be used in one of two modes: i) pure sampling, or ii) optimization. The main difference between these two modes is that in pure sampling, the parameter T is the same for all Gibbs sampling iterations, whereas in optimization (simulated annealing), T gradually decreases to help faster convergence to a final solution [29].

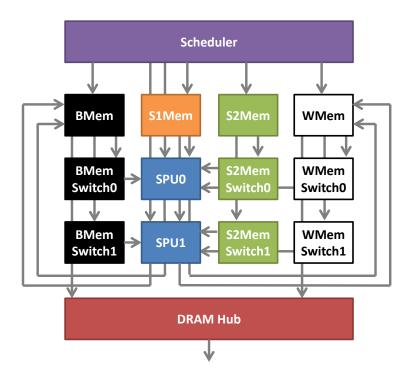

FIGURE 3.5: Architecture of an SPE with two SPUs. For the sake of clarity, non-local outgoing communications from BMem, WMem, and S2Mem modules and incoming communications to BMem Switches, WMem Switches, and S2Mem Switches have been omitted. BMem and WMem send data to the BMem and WMem Switches in the top, down, left, and right neighbors. S2Mem sends data to the S2Mem Switches in all the eight neighbors shown in Figure 3.3a.

The implication of this difference is that in pure sampling mode, when the algorithm converges to a final solution, the estimated distribution of a RV can be generated by collecting the histogram of the latest N samples. Since in this work we are interested in the uncertainty quantification capability of MCMC, we only focus on the pure sampling mode. However, the proposed accelerator can operate in optimization mode as well.

#### 3.3.3 Stochastic Processing Element

An SPE incorporates the components that carry out the operations needed to feed the necessary data to SPUs every cycle and write back the result of their computations to the LMem. These operations include sequencing through RVs and generating

memory addresses corresponding to the singleton and neighborhood data, reading the data at those addresses and passing them to the appropriate SPU, and writing the results of the computations back to the correct addresses in LMem. Furthermore, to maintain the histogram of labels, it might be necessary that while writing data back to LMem, some data should be sent to the off-chip DRAM. Figure 3.5 shows the SPE's components and the interactions between them. The next section is dedicated to describing the various components inside an SPE, followed by a more detailed explanation of scheduling and different types of memory in the SPE.

#### Components

Scheduler: This component's main job is to generate the update schedule and coordinate the operations of most of the other components in an SPE. It interacts with SPUs and various memory blocks, and its functionalities include sending the SPUs some parameters including the T in MCMC equations in Figure 2.1, and other information such as whether a pixel is on the boundary or whether it is a black or a white pixel (to determine the destination of the computations result). It also sends the computed addresses to different memory blocks, so that they can return the requested data to the SPU.

Singleton 1 Memory: Denoted by S1Mem in Figure 3.5, it stores singleton 1 data as the name suggests, or in the example of motion estimation in Section 3.1.1, the data in the blue box in Figure 3.1. It receives addresses from the Scheduler and sends data to the SPUs once for every RV.

Singleton 2 Memory: Similar to S1Mem, it is referred to as S2Mem in Figure 3.5, and stores singleton 2 data (i.e., the data in the green box in Figure 3.1). Because each singleton 2 corresponds to an individual label, as opposed to singleton 1 which is fixed for all labels of the same RV, S2Mem receives a base address from the Scheduler, and computes addresses for the appropriate singleton 2 data point for

each label by reading from an offset look-up table (LUT) populated by the runtime in an application-by-application basis. For instance, in the case of motion estimation, the LUT stores the offsets that define the  $7 \times 7$  window shown in Figure 3.1. It then sends that data to S2Mem Switches for every label. Since this data is needed for every label at every SPU, it is required that multiple reads from different addresses be issued at the same cycle. We address this problem by devising a banking scheme that is described in Section 3.3.3. Both singleton memories are read-only, meaning they get initialized in the beginning by the runtime and will never change throughout the execution.

Singleton 2 Switch: These switches receive data from the appropriate S2Mem, i.e., either the local S2Mem or one of the memories in one of the eight neighbors, and send it to the SPUs they are connected to.

Label Memories: BMem and WMem in Figure 3.5, together form the LMem. These memories store the results of the computations done by the SPUs. They receive addresses from the Scheduler to send neighborhood data to the corresponding switches, which in turn send those data to the SPUs. They also receive the new labels from SPUs. Although neighborhood data is needed only once per RV, due to the model's structure, multiple reads must be issued simultaneously to provide the data necessary for beginning the computations to the SPUs. We solve this problem by banking the LMem and pipelining accesses to them. In addition to storing the labels computed by the SPUs, LMem is also part of the hybrid on-chip/off-chip memory system that stores the information required for generating the labels histogram. LMem is explained in more detail in Section 3.3.3.

Label Switches: These switches are similar in functionality to S2Mem Switches, i.e., they receive neighborhood data from the local LMem as well as the LMems in the top, down, left, and right SPEs and pass them to their corresponding SPU.

## Updating Order and Inter-variable Parallelism

In general, MCMC is a sequential algorithm since updating each RV depends on the latest value of all other RVs. However, as explained in Section 3.1.1, in the first-order MRF model, each RV is only conditionally dependent on its top, down, left, and right neighbors. This means there is an opportunity to develop a chromatic schedule for updating conditionally independent variables in parallel and thus, significantly reduce the execution time. For first-order MRF, this schedule is a simple checkerboard scheme which divides the random field into a black (BMem) and a white (WMem) subset, where all RVs in each subset are independent [31, 46, 51]. In our proposed accelerator, the Scheduler in each SPE is responsible for generating this schedule. The Scheduler first goes through all black RVs, then flushes the pipeline of all other components, and repeats the same process for white RVs.

Another benefit of this chromatic schedule is that it puts restrictions on access types to different parts of LMem, i.e., while black variables are being updated, there will be no writes issued to WMem and vice versa. This allows for simplifying the memory structure by dividing it into a black and a white region, knowing that the Scheduler takes care of avoiding conflicting accesses to these regions.

## Singleton Memory Structure for Multiple SPUs

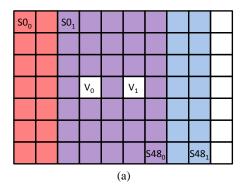

According to the MCMC details explained in Section 3.1.1, there are potentially two types of singleton data, both of which are stored in read-only memories: 1) singleton 1, which is always present and is required once for a RV, and 2) singleton 2, which, if present, is required for each possible label a RV can take on. The implication of singleton 2's access pattern is that if we decide to have more than one SPU in an SPE to amortize the area of the Scheduler and other control logic, servicing singleton 2 reads becomes a challenge. Figure 3.6a illustrates this problem with an example of two SPUs in an SPE running in parallel. Multiple pieces of singleton 2 data at

FIGURE 3.6: (a) An example of the singleton 2 access pattern for motion estimation in an SPE with two SPUs. Boxes shaded in red and purple illustrate the singleton 2 window for RV  $V_0$ , and boxes shaded in purple and blue show that window for  $V_1$ , and (b) the proposed banking scheme to solve the multiple simultaneous accesses issue. Each color represents one bank. Locations denoted by  $S0_0$  and  $S0_1$  must be accessed together, and so is the case for  $S48_0$  and  $S48_1$ .

different addresses must be read at the same cycle. There are three possible solutions to accommodate this access pattern:

- 1. S2Mem must support a read size larger than one singleton 2, and an intermediate register must handle the feeding of data to the appropriate SPU. This option also allows exploiting the temporal locality of singleton 2, i.e., a piece of data can be read once and used multiple times if it is required for multiple RVs. However, determining when to issue new reads, shifting and moving data around, and developing an update schedule that matches this design make it complicated, particularly due to the application-specific patterns of singleton 2 accesses.

- 2. S2Mem must be a multi-port structure to be able to straightforwardly read the required data from it. Nevertheless, multi-port memories are area- and power-hungry and are generally not preferable [99]. This option also does not take advantage of singleton 2's temporal locality.

- 3. S2Mem must be divided into separate banks with only one port each, that are

FIGURE 3.7: Memory banking scheme for white and black sections of LMem. Note that while updating RVs in BMem, their neighbors are in WMem and vice versa.

accessed simultaneously. Similar to the previous solution, the drawback of this design is that it too necessitates reading the same piece of data multiple times. However, it allows for a simpler Scheduler and memory structure and therefore, we choose this option for S2Mem.

Our proposed banking scheme exploits the knowledge of the update order discussed in Section 3.3.3. More specifically, we take advantage of the stride of two consecutive RVs in the same row. Because we know the next RV will always be two locations ahead and the singleton 2 access pattern is the same for all RVs, it logically follows that the next singleton 2 will also be two locations ahead. Thus, we put every two columns of singleton 2 in a separate bank, for a total number of banks equal to the number of SPUs inside the SPE. Figure 3.6b demonstrates this for an example SPE with two SPUs. The runtime is responsible for correctly populating these banks.

#### Labels Memory and Labels Log

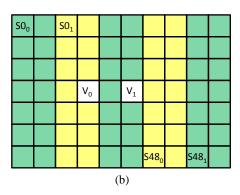

Similar to singleton 1, neighborhood data is needed once for each RV (Section 3.1.1). Nevertheless, since in the first-order MRF the neighborhood structure consists of four RVs, a simple monolithic single-port memory does not accommodate the requirements of the model. A key difference with S2Mem, though, is that neighborhood data is needed only once for each RV. Therefore, reads to the LMem can be

pipelined to provide data to multiple SPUs in an SPE. To overcome the challenge of accessing four locations in LMem simultaneously, we use a memory banking scheme shown in Figure 3.7. This pattern is repeated to cover the input. It ensures that for every RV, its top, down, left, and right neighbors reside in unique banks.

In addition to storing the labels data, LMem is also a part of the on-chip/off-chip memory system that collects the labels histogram for uncertainty quantification. Collecting an accurate histogram needs a counter per each possible label, in our case 64, and each counter must be able to hold the maximum number of iterations, which could be 10-12 bits. Storing such a huge amount of data on chip is neither practical nor efficient. Fortunately, it is not necessary either.

As Figure 3.2 shows, a significant portion of RVs take on only a few unique labels after the warp-up period has passed. This inspired us to have room for a few labels and their corresponding counters on chip, and once a counter is saturated or a new label is selected that is not present in the LMem, send a message consisting of the evicted label's ID, the RV's address, and the count associated with it, to an off-chip memory. This data is stored in the form of a log, which at the end of the execution is processed by the runtime and translated into a histogram. The operation of this memory structure is similar to a write-back, write-allocate, no fetch-on-write cache. The main advantage of such a design is that unlike normal caches where data travels in both directions (i.e., on-chip to off-chip and vice versa), here data only go out from on-chip memory and hence, with deep enough FIFOs to store the messages until they can be sent to the off-chip memory, the computation units will not be forced to stall.

The remaining challenges are: 1) choosing an efficient replacement policy, and 2) determining the optimal size of the on-chip LMem (i.e., how many label+counter pairs to keep per RV). We considered two replacement policies, Least Frequently Picked (LFP), and Least Recently Picked (LRP). Intuitively, LFP makes the most sense because we want to keep the label that is selected most often on-chip. However,

FIGURE 3.8: Maximum values of Equation 3.5 for three input data sets for stereo vision [9] and motion estimation [6] per LMem size. The replacement policy is least recently picked.

it is both more complicated to implement and more sensitive to the time we start to collect the histogram. To be more specific, if we start collecting the histogram too soon, i.e., before the end of the warm-up period, it is possible that a label which is not among the top few most frequently picked labels overall is picked enough times that it prevents the actual frequent labels from remaining in the on-chip memory. LRP, however, avoids this by evicting the aforementioned label because it is not selected anymore after the warm-up period. For these reasons, we choose LRP as the replacement policy.

To determine the size of the on-chip memory, we must take into account the trade-off between this size and the off-chip bandwidth and the size of the off-chip log. Ideally, we want the smallest on-chip memory that the off-chip bandwidth allows. We use Equation 3.5 to arrive at this size:

$$\frac{\frac{\#SPUs}{\#Labels} * EvictionRate * MessageSize}{Bandwidth} < 1$$

(3.5)

#SPUs is the total number of SPUs in the accelerator, #Labels is the number of possible labels a RV can take on (an application-specific value), EvictionRate is the rate at which labels are evicted to off-chip memory, MessageSize is the size of the

Table 3.1: Values used to calculate Equation 3.5 for Figure 3.8.

| Parameter    | Value                                            |  |  |  |  |

|--------------|--------------------------------------------------|--|--|--|--|

| #SPUs        | 2048                                             |  |  |  |  |

| #Labels      | Stereo Vision: 28, 30, 56; Motion Estimation: 49 |  |  |  |  |

| Message Size | 32 bits                                          |  |  |  |  |

| Bandwidth    | 512 bits/cycle                                   |  |  |  |  |

messages in bits, and *Bandwidth* is the available off-chip bandwidth. Equation 3.5 indicates that the amount of off-chip communication must not exceed the available bandwidth. Figure 3.8 shows the maximum value of Equation 3.5 for three input data sets for stereo vision [9] and motion estimation [6] for different sizes of LMem (Table 3.1 lists the values used to compute the result of Equation 3.5). To generate this graph, we first collect a trace of the labels of all RVs at every iteration. We then process this trace to simulate the behavior of our proposed LMem with sizes of 1-8 label+counter pairs per RV. The figure indicates that with a LMem large enough to hold only two label+counter pairs per RV, the off-chip bandwidth utilization will not exceed 60% of the available bandwidth. Therefore, we select two label+counter pairs per RV.

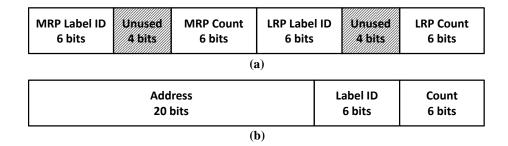

Given the number of label+counter pairs per RV, and the number of RVs that the accelerator supports (1M RVs in this example), Figure 3.9 shows the structure of a LMem entry and a message sent to off-chip memory. It is possible to change the width of the counter and the address fields depending on the size of the target input sets. It is also possible to reduce the required bits for addressing by directing messages from certain SPEs to pre-defined offsets in the off-chip DRAM.

With this proposed scheme, writing to the LMem is transformed to a read-modifywrite, where depending on the current labels in the target LMem entry and the new label, a re-ordering of the data in the entry or sending a message to the off-chip memory may be needed.

FIGURE 3.9: Structure of (a) a LMem entry, and (b) a message to off-chip memory, in which the RV address and label ID are together the bin identifier in the histogram. For the LMem entry, we assume a 32-bit word due to FPGA limitations. More area savings are possible in ASIC design.

## **Algorithm 1** Writing to the label memory.

```

1: procedure WriteLabel(addr, new_lbl)

\{\text{mrp\_lbl}, \text{mrp\_cnt}, \text{lrp\_lbl}, \text{lrp\_cnt}\} \leftarrow \text{mem[addr]}

3:

\mathbf{if} \text{ new\_lbl} = \text{mrp\_lbl } \mathbf{then}

if mrp_cnt = MAX_VALUE then

4:

\{addr, mrp\_lbl, MAX\_VALUE\} \rightarrow DRAM

5:

mem[addr] \leftarrow \{mrp\_lbl, 1, lrp\_lbl, lrp\_cnt\}

6:

7:

else

mem[addr] \leftarrow \{mrp\_lbl, mrp\_cnt + 1, lrp\_lbl, lrp\_cnt\}

8:

9:

else if new\_lbl = lrp\_lbl then

if lrp_cnt = MAX_VALUE then

10:

\{addr, lrp\_lbl, MAX\_VALUE\} \rightarrow DRAM

11:

mem[addr] \leftarrow \{lrp\_lbl, 1, mrp\_lbl, mrp\_cnt\}

12:

13:

else

mem[addr] \leftarrow \{lrp\_lbl, lrp\_cnt + 1, mrp\_lbl, mrp\_cnt\}

14:

else

15:

\{addr, lrp\_lbl, lrp\_cnt\} \rightarrow DRAM

16:

mem[addr] \leftarrow \{new\_lbl, 1, mrp\_lbl, mrp\_cnt\}

17:

```

#### 3.3.4 Accelerator Topology

There are two networks in our proposed accelerator, one that connects the SPEs which transfers label and singleton 2 data (Section 3.3.4), and another that connects the label memories in SPEs to the interface to off-chip memory (Section 3.3.4). These two networks carry traffic with different characteristics and requirements, and thus, have different topologies.

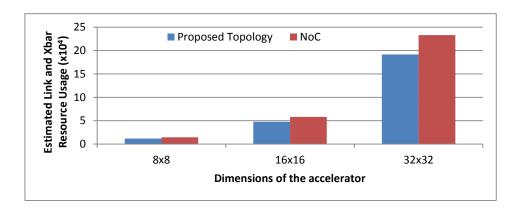

FIGURE 3.10: Comparison of the estimated amount of resources needed for links and crossbars in the proposed topology and a 2-D mesh NoC.

#### SPE Network

Communications among SPEs follow a regular pattern, e.g., when an SPU inside an SPE needs a piece of data that resides in the left neighbor, the right neighbor also needs a piece of data at that same address in the current SPE. This is true for both label data and singleton 2 data communication, and is due to the characteristics of the first-order MRF model and the even distribution of work to SPEs guaranteed by the runtime.

Due to this regular pattern of communication, we propose to use a topology in which every SPE is connected to its top, down, left, and right SPEs for transferring label data, and to all eight nearest neighbors (as shown in Figure 3.3a) to communicate singleton 2 data. The runtime then ensures that all the data an SPE could possibly need reside in those SPEs to which it is directly connected. This way, there is no need for a full-fledged Network-on-Chip (NoC). Whenever SPEs need data from their neighbors, they also push data in the opposite direction because their neighbor needs the same type of data. This ensures a stall-free execution. Additionally, this topology avoids the area overhead of a NoC router. Nevertheless, crossbars and links are still required for moving data around. Figure 3.10 demonstrates the estimated

amount of resources needed for our proposed topology compared to a 2-D mesh NoC, for accelerators with three different dimensions in which each SPE has 2 SPUs. The values are derived from Equations 3.6, 3.7, 3.8, and 3.9, in which D denotes the dimension of the accelerator, S shows the number of SPUs per SPE, NN refers to our proposed topology, and NoC indicates the 2-D mesh NoC. Also, I:O means a crossbor with I input and O output ports. To estimate the amount of resources needed for a crossbar, we simply multiplied its number of input and output ports. We substituted S with 2 and added the two values for each topology to generate Figure 3.10. Although this is not an accurate measure of the required resources (for instance, one could argue that links and crossbars should not have the same weight), combined with the reduced design complexity enabled by our proposed topology, we chose that over a generic NoC.

$$NN_{Links} = 2(2(D-1)D(S+1) + 2(D-1)^2S)$$

(3.6)

$$NN_{XB} = D^{2}(2(4:8) + (S:9S) + 8(2:S) + (9S:S))$$

(3.7)

$$NoC_{Links} = 2(2(D-1)D(S+1))$$

(3.8)

$$NoC_{XB} = D^{2}(2(4:8) + (S:5S) + 8(2:S) + (5S:5S))$$

(3.9)

## DRAM Hub Network

Unlike the regular communications between SPEs which depending on the application can be intensive during some periods of execution, communications between SPEs and DRAM Hubs are irregular and designed to be infrequent. Although we cannot guarantee the latter is always the case, our workload characterization discussed in Section 3.3.3 demonstrates that by carefully designing the memory system, we can achieve this in practice. Guided by this assumption, we use a tree topology for the DRAM Hub network, as shown in Figure 3.3b. Every four SPEs are connected to one DRAM Hub, forming a region, and then every four DRAM Hubs are connected

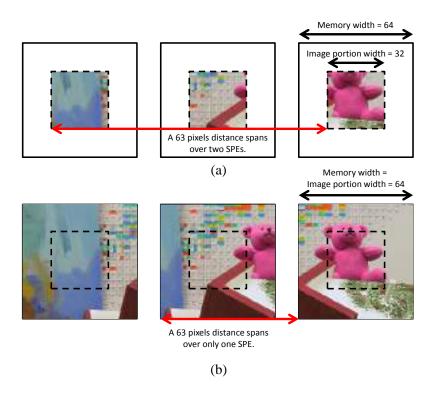

FIGURE 3.11: (a) Example of an input set for stereo vision in which communications with SPEs farther than one hop is necessary to transfer singleton 2 data, and (b) solving this problem by replicating singleton 2 data.

to each other. This pattern continues up until the interface with the off-chip DRAM. This topology is scalable and does not cause communication with the DRAM to become a bottleneck. Furthermore, communication with the DRAM is one-way during the execution, i.e., data only flows from the accelerator toward DRAM. Therefore, the high latency of off-chip communication does not stall the execution pipeline of the accelerator. At the DRAM interface, messages are aggregated to form 512-bit lines and are written to the DRAM. A log index is kept at the DRAM interface which is both used for writing new values to DRAM throughout the execution, and reading valid values from the DRAM at the end of execution.

#### 3.3.5 Runtime

The runtime is responsible for handling memory allocation, parameter initialization, data padding when necessary, and data placement and movement. In this section, we only discuss data padding and data placement because the other operations are only a matter of implementation. Data padding might be necessary depending on the input size, because work must be distributed among SPEs evenly as the correct communication of data between SPEs relies on this assumption. Another assumption that our proposed communication scheme builds upon is that all the data an SPE might possibly need, whether label or singleton 2 data, must be available in at most a single hop distance. Although this assumption always holds for label data (only the labels of immediate neighboring RVs are needed), it might not necessarily hold for singleton 2 depending on its access pattern and how small the input data set is. Figure 3.11a illustrates this with an example. In this example, the application is stereo vision [9] in which the singleton 2 accesses could reach 63 locations to the left of any given RV. In this case, if the width of the portion of the input assigned to each SPE is smaller than the reach of singleton 2, then communication longer than one hop will be necessary. Fortunately, replicating the singleton 2 is a simple fix for this problem and the runtime can handle it.

#### 3.3.6 Limitations and Future Work

Some limitations of our proposed accelerator are inherent to the specific Gibbs sampling algorithm selected, e.g., the lack of support for continuous RVs. Some other limitations are due to our design and implementation. For example, because of the design choice to represent labels with six bits, the proposed accelerator cannot support problem instances with more than 64 labels. However, 64 labels is enough for many applications [51, 79], and expanding the number of supported labels is future work. In addition, previous work shows that slightly increasing the bit width in some

places in the SPU datapath increases the result quality to be closer to floating-point software implementations. Incorporating those changes in our design is future work, and we expect the effects on the area to be small.