### TECHNIQUES FOR HIGH BANDWIDTH, LOW LATENCY INTERCONNECTION NETWORK OPERATION AT HIGH OFFERED LOADS

by

MITHUNA S. THOTTETHODI

Department of Computer Science

Duke University

Date: 10 - 23 - 07

Approved:

Ahvin R. Lebeck, Sapervisor

Shubhendu S. Mukherjee, Supervisor

Jeffrey S. Chase

Gershon Kedem

Amin M. Vahdat

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

2002

UMI Number: 3092889

#### UMI Microform 3092889

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **ABSTRACT**

(Computer Architecture)

# TECHNIQUES FOR HIGH BANDWIDTH, LOW LATENCY INTERCONNECTION NETWORK OPERATION AT HIGH OFFERED LOADS

by

MITHUNA S. THOTTETHODI

Department of Computer Science Duke University

Approved:

Alvin R. Lebeck, Supervisor

Alvin Shubhendu S. Mukherjee, Supervisor

Jeffrey S. Chase

Ors Stadd

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

2002

#### **Abstract**

Large-scale, cache coherent, distributed shared memory multiprocessors constitute an important and growing segment of the server market. Overall performance in such systems depends on compute performance, memory performance, and interconnection network performance. Interconnection network performance lies on the critical path of remote misses (which is the key communication mechanism in distributed shared memory multiprocessors) and consequently, poor network performance can significantly reduce overall system performance.

While there are a number of techniques that have enhanced interconnection network performance significantly, known performance problems due to network saturation at high offered loads that result in poor bandwidth and high latencies continue to pose a challenge to system designers. The symptoms of the problems are as follows: the achieved throughput goes up with offered load steadily till a certain point beyond which there is a sudden and significant drop in throughput (and a corresponding increase in latency). This occurs due to imbalances in network resource usage as well as the lack of fast feedback resulting in routers making decisions using only locally available information that may be globally detrimental.

Solutions to this problem can be broadly classified into two categories: (a) congestion control solutions and (b) load balancing solutions. This thesis proposes and evaluates one congestion control technique and two load balancing techniques to overcome the performance problems in k-ary, n-cube networks at high loads.

The first technique is a self-tuned congestion control mechanism—Tune—that has two key features: (a) it uses global congestion information to throttle the offered load when saturation is imminent and thus ensures that the network stays in the high-bandwidth, low latency region of operation and (b) it has a global throughput-driven

self-tuning mechanism that enables it to adapt to various communication patterns. Simulations with various communication patterns show that *Tune* is able to prevent the sudden drop in performance that occurs at saturation. *Tune* can be used with both wormhole and virtual cut-through switched networks.

The second technique—congestion-aware via routing—attempts to achieve load balancing to prevent saturation. In this technique, packets are directed away from congested network regions using global congestion information by requiring them to go via certain intermediate nodes. I demonstrate that this technique achieves limited improvements for non-uniform traffic patterns. Simulations show that the benefits of congestion aware via-routing, even with perfect global knowledge, are not compelling. These results illustrate the inherent limits of load balancing in the minimum rectangle and this key insight leads to the next technique.

Finally, I propose a new non-minimal routing (i.e. packets can be routed on hops that take them farther from the destination) algorithm—BLAM—that goes beyond the constraints of minimal routing which I assumed for the first two techniques. Non-minimal routing can deliver better performance because of the additional routing flexibility. However, because packets can go farther from the destination, livelock is a concern in non-minimal routing. Existing non-minimal routing algorithms either require costly and non-scalable implementations of router-wide priorities or they offer only probabilistic guarantees of livelock-freedom. In contrast, BLAM achieves the higher performance of non-minimal routing by using lazy misroutes without the drawbacks, i.e., it offers deterministic guarantees of livelock freedom by using limited misroutes. Simulations show that BLAM achieves performance similar to chaotic routing, which is a high-performance non-minimal routing algorithm with only probabilistic guarantees of livelock freedom.

# Contents

| A  | bstra  | act     |                                                                          | 111     |

|----|--------|---------|--------------------------------------------------------------------------|---------|

| Ĺ  | ist of | f Table | es<br>S                                                                  | viii    |

| Li | ist of | f Figur | es                                                                       | ix      |

| Α  | ckno   | wledge  | ements                                                                   | xiii    |

| 1  | Int    | roduct  | ion                                                                      | 1       |

|    | 1.1    | Contr   | ibutions                                                                 | 4       |

|    | 1.2    | Thesi   | s Organization                                                           | 8       |

| 2  | Bac    | ekgrou  | nd and Related Work                                                      | 9       |

|    | 2.1    | Backg   | ground                                                                   | 9       |

|    |        | 2.1.1   | Network Topology                                                         | 10      |

|    |        | 2.1.2   | Base Router Architecture                                                 | 10      |

|    |        | 2.1.3   | Deadlock Handling in Minimal Adaptive Routers with Escape Paths          | 12      |

|    | 2.2    | Relate  | ed Work                                                                  | 13      |

|    |        | 2.2.1   | Congestion Control                                                       | 13      |

|    |        | 2.2.2   | Load Balancing in the Minimum Rectangle                                  | 16      |

|    |        | 2.2.3   | Deadlock, Livelock and Performance Issues in Nonminimal Adaptive Routers | -<br>18 |

| 3  | Tun    | ie: A S | Self-tuned Congestion Control Mechanism                                  | 21      |

|    | 3.1    | Gathe   | ering global information                                                 | 22      |

|    |        | 3.1.1   | Implementing Global Information Gather                                   | 23      |

| 3.2 Self-Tuning Mechanism |                   |                                                                     | 27 |

|---------------------------|-------------------|---------------------------------------------------------------------|----|

|                           |                   | 3.2.1 Hill Climbing                                                 | 28 |

|                           |                   | 3.2.2 Avoiding Local Maxima                                         | 30 |

|                           |                   | 3.2.3 Summary                                                       | 31 |

|                           | 3.3               | Methodology                                                         | 32 |

|                           | 3.4               | Simulation Results                                                  | 34 |

|                           |                   | 3.4.1 Overall Performance                                           | 35 |

|                           |                   | 3.4.2 Obtaining Global Information                                  | 41 |

|                           |                   | 3.4.3 Varying <i>Tune</i> 's increment/decrement values             | 44 |

|                           |                   | 3.4.4 Bursty Traffic                                                | 44 |

|                           |                   | 3.4.5 Distributing Information using Meta Packets                   | 50 |

|                           | 3.5               | Summary                                                             | 54 |

| 4                         | Loa               | d Balancing in the Minimum Rectangle                                | 56 |

|                           | 4.1               | Via Routing: The Mechanism                                          | 57 |

|                           | 4.2               | Min-triangle and Random-triangle Via Selection Policies             | 59 |

|                           | 4.3               | Min-Corridor Via Selection Policy                                   | 60 |

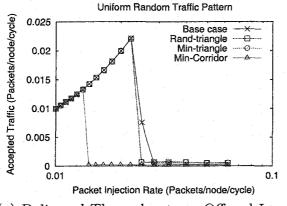

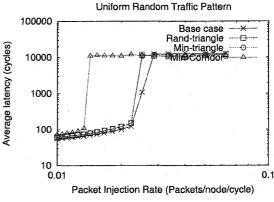

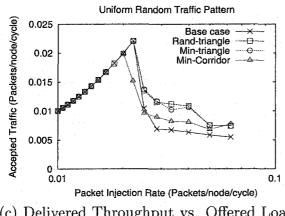

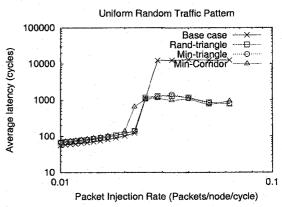

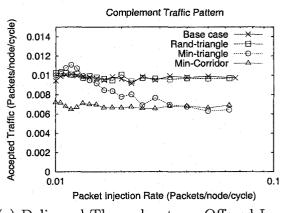

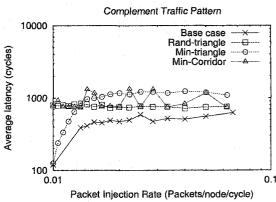

|                           | 4.4               | Via-Routing Results                                                 | 62 |

|                           | 4.5               | Summary                                                             | 64 |

| 5                         | $\mathbf{BL}^{A}$ | AM routing                                                          | 74 |

|                           | 5.1               | Deadlocks, Livelocks and Performance in Nonminimal Adaptive Routing | 74 |

|                           | 5.2               | Misroutes                                                           | 77 |

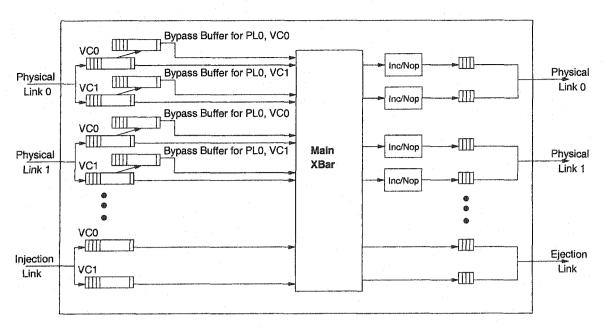

|                           | 5.3               | Bypass buffers                                                      | 79 |

|                           |                   | 5.3.1 Implementing Distributed Bypass Buffers                       | 81 |

|       |                    | 5.3.2         | Summary                              | 4 |

|-------|--------------------|---------------|--------------------------------------|---|

|       | 5.4                | Evalu         | ation Methodology                    | 5 |

|       |                    | 5.4.1         | Simulation Details                   | 5 |

|       |                    | 5.4.2         | Open vs. Closed Loop                 | 6 |

|       |                    | 5.4.3         | Network Workload                     | 7 |

|       |                    | 5.4.4         | Network and Router Architectures     | 8 |

|       | 5.5                | Simul         | ation Results                        | 9 |

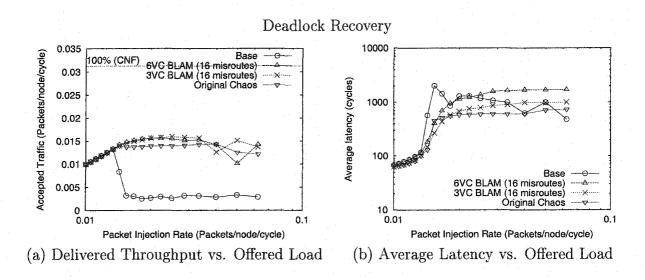

|       |                    | 5.5.1         | Overall Performance                  | 0 |

|       |                    | 5.5.2         | Varying the Misroute Limit           | 8 |

|       |                    | 5.5.3         | Effect of Adding Bypass Buffers      | 4 |

|       |                    | 5.5.4         | M-misroute, Adaptive router          | 4 |

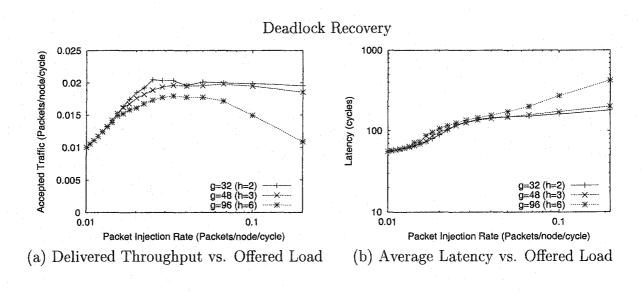

|       |                    | 5.5.5         | Varying Packet Size and Network Size | 2 |

|       | 5.6                | Summ          | ary 11:                              | 3 |

| 6     | Cor                | clusio        | n 12:                                | 3 |

|       | 6.1                | Summ          | ary                                  | 3 |

| Bi    | iblios             | graphy        | 120                                  | 6 |

|       |                    |               |                                      | 3 |

| B-K 1 | E . A . H. S. C. B | W B IF B TA / | 1.3.                                 |   |

# List of Tables

| 3.1 | Tuning decision table                        | 29 |

|-----|----------------------------------------------|----|

|     |                                              |    |

| 5.1 | Design variables for various routing schemes | 8  |

# List of Figures

| 1.1  | Distributed Shared Memory Systems with k-ary, n-cube networks                                              | 2  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Interconnection network on Critical Path                                                                   | 3  |

| 1.3  | Performance Breakdown at Network Saturation, 16x16 2D network, adaptive routing, deadlock recovery         | 4  |

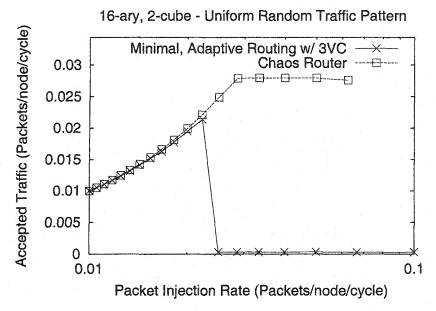

| 1.4  | Minimal Adaptive Routing w/deadlock recovery and Chaotic Routing                                           | 5  |

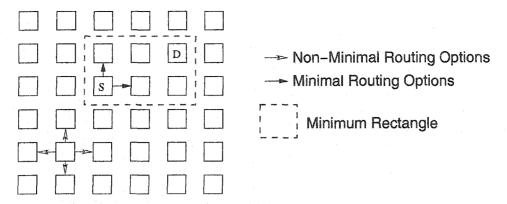

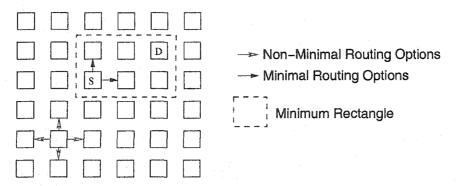

| 1.5  | Routing Options Minimal vs. Non-minimal                                                                    | 7  |

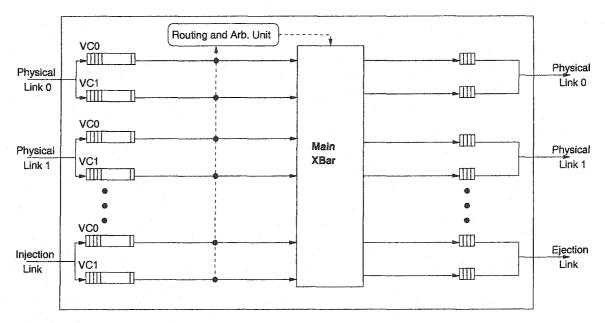

| 2.1  | Base Minimal, Adaptive Router with Multiple Virtual Channels                                               | 11 |

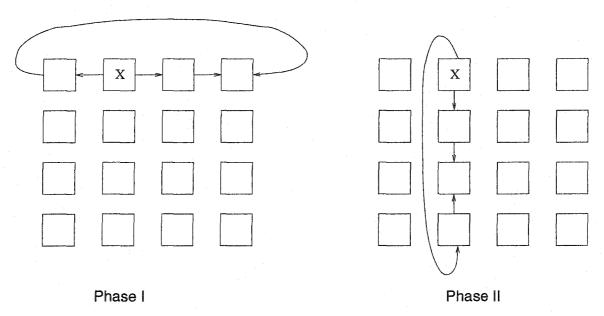

| 3.1  | Dimension-wise global aggregation.                                                                         | 25 |

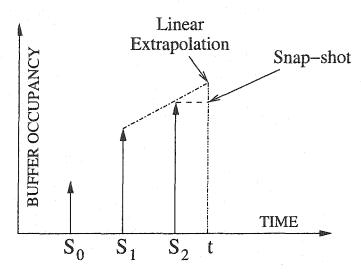

| 3.2  | Estimation of global congestion: Previous Snapshot vs. Linear Extrapolation                                | 26 |

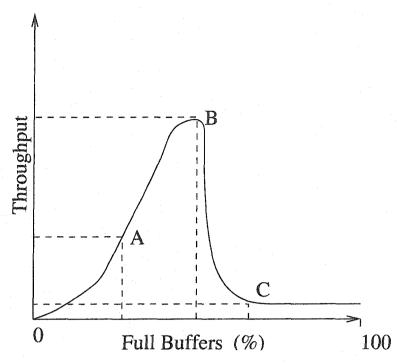

| 3.3  | Throughput vs. Full Buffers                                                                                | 28 |

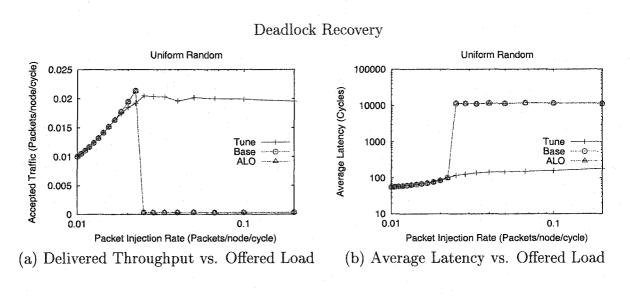

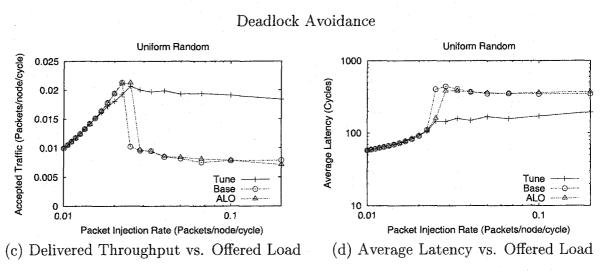

| 3.4  | Overall Performance With Random Traffic                                                                    | 37 |

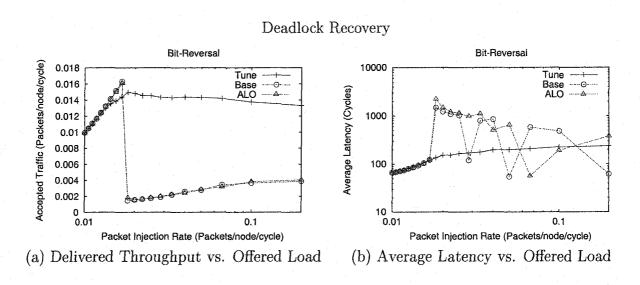

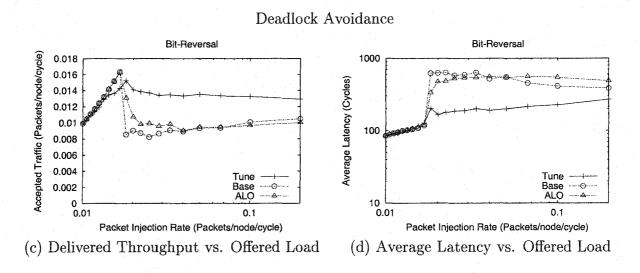

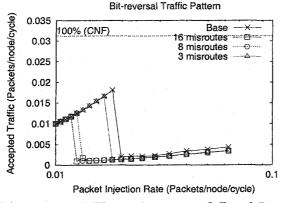

| 3.5  | Overall Performance With Bit-Reversal Traffic Pattern                                                      | 38 |

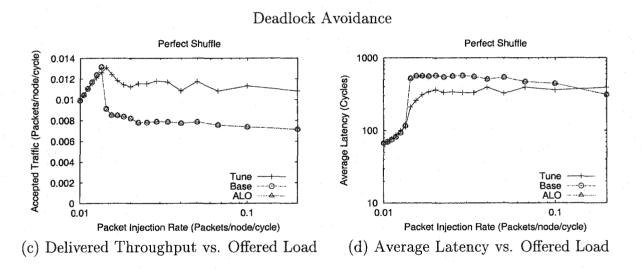

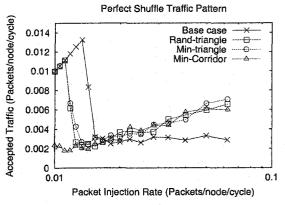

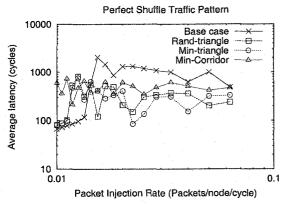

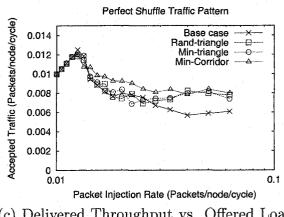

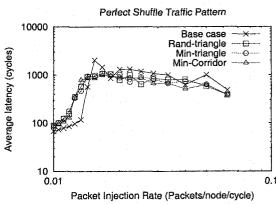

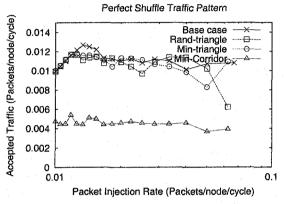

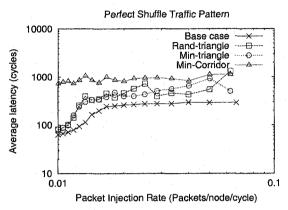

| 3.6  | Overall Performance With Perfect-Shuffle Traffic Pattern                                                   | 39 |

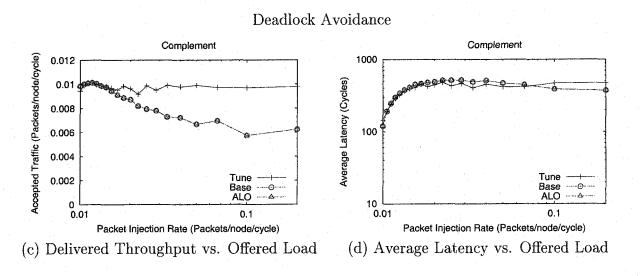

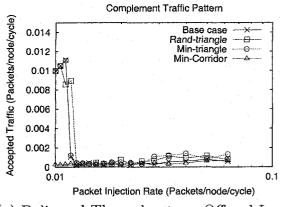

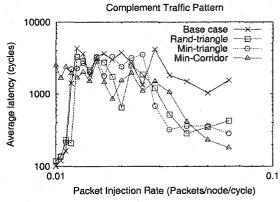

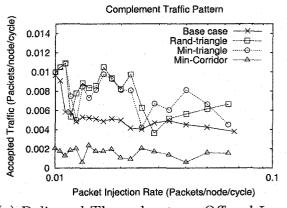

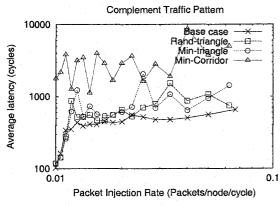

| 3.7  | Overall Performance With Complement Traffic Pattern                                                        | 40 |

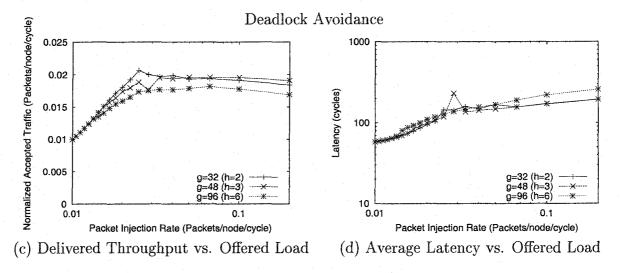

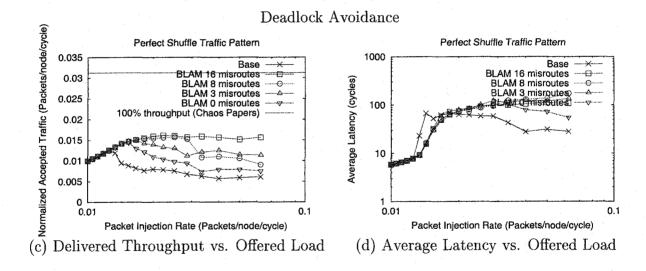

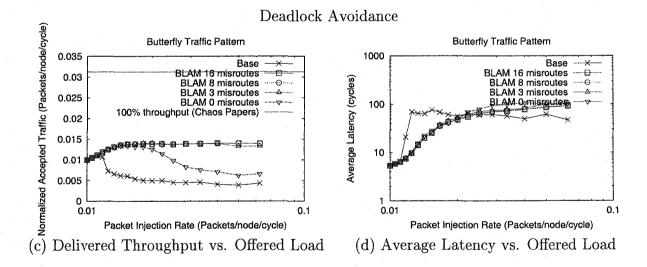

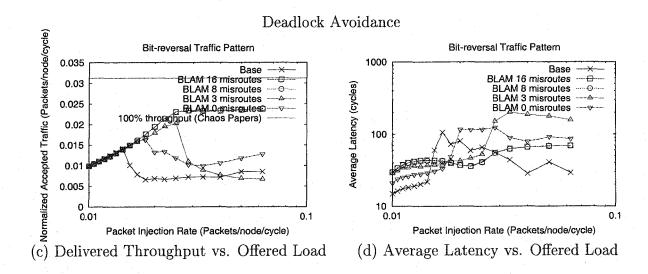

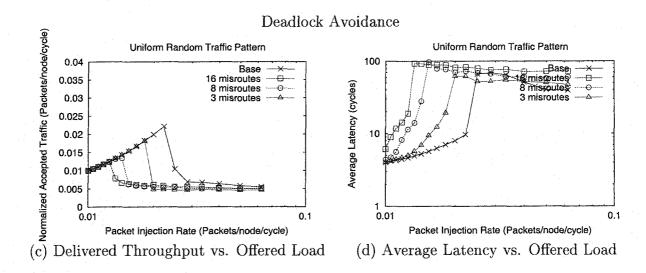

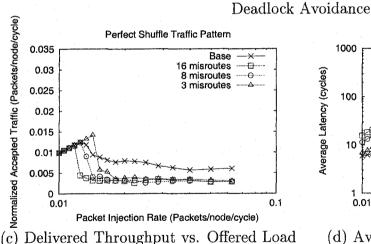

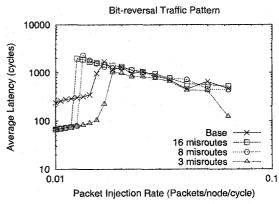

| 3.8  | Effect of Global Information Gathering Delays for Deadlock Recovery (a & b) and Deadlock Avoidance (c & d) | 46 |

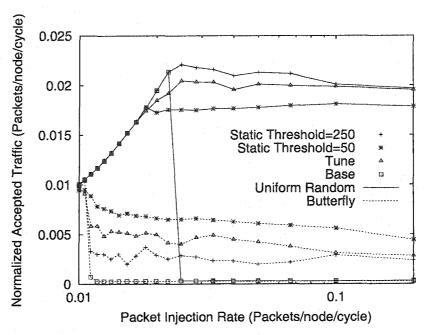

| 3.9  | Static Threshold vs. Tuning                                                                                | 47 |

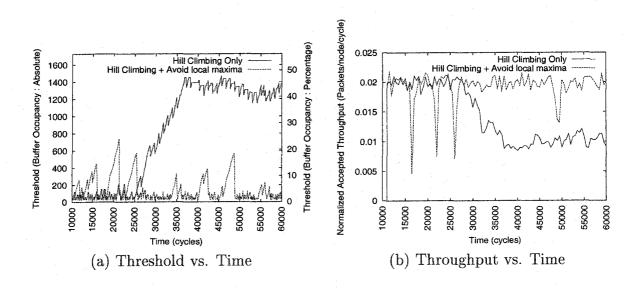

| 3.10 | Self-Tuning Operation: An Example                                                                          | 47 |

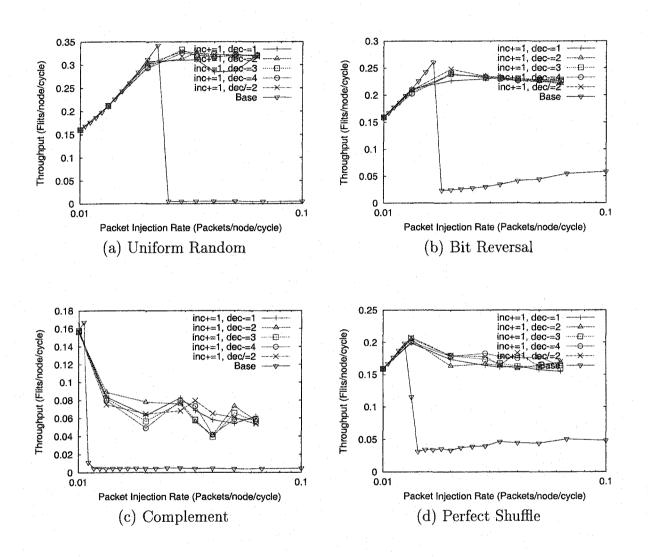

| 2 11 | Choice of increment /decrement quanta                                                                      | 48 |

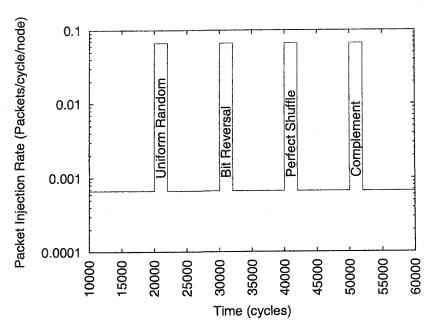

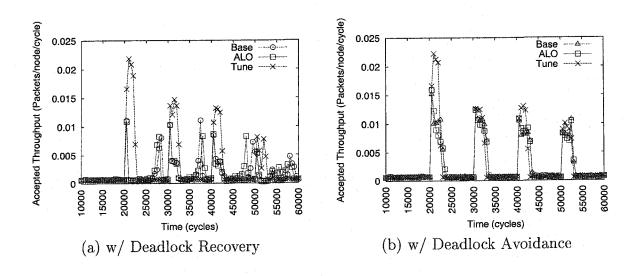

| 3.12 | Offered bursty load                                              | 49 |

|------|------------------------------------------------------------------|----|

| 3.13 | Performance with Bursty Load : Delivered Throughput              | 49 |

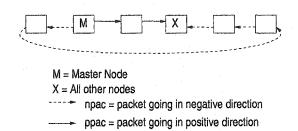

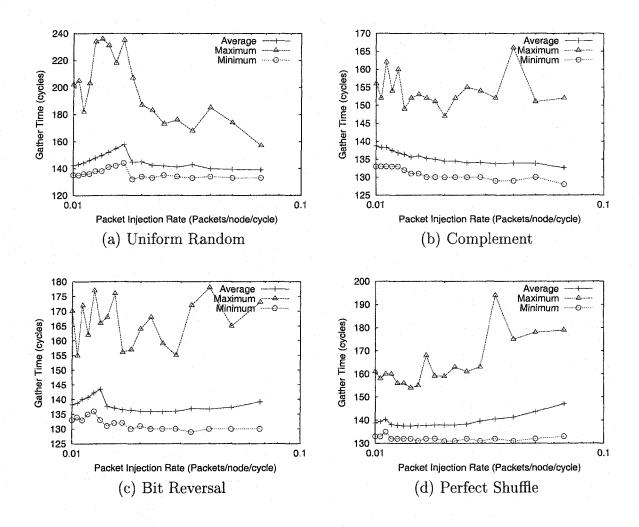

| 3.14 | Row aggregation using two meta packets                           | 51 |

| 3.15 | Minimum, Maximum and Average gather times using meta packets .   | 52 |

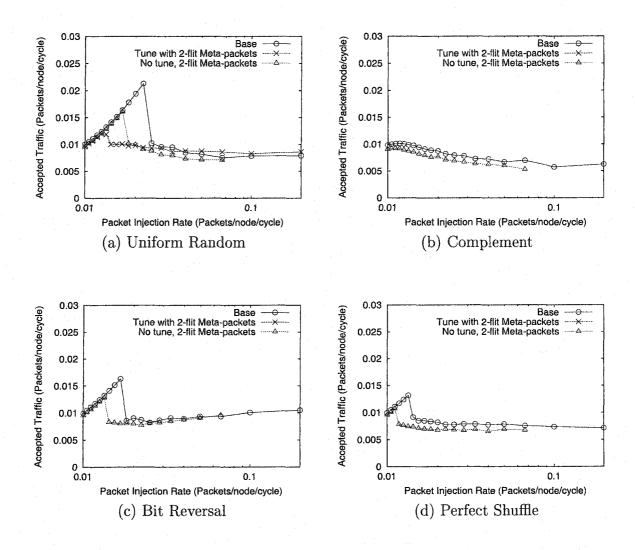

| 3.16 | Effect of Meta-packets and Tuning on Throughput                  | 53 |

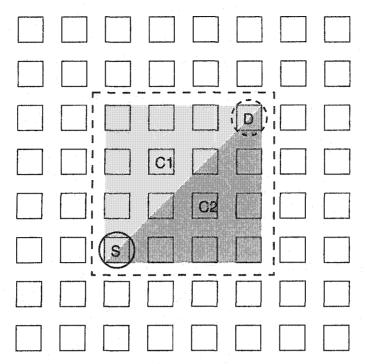

| 4.1  | Via Routing: Upper and Lower Triangles                           | 60 |

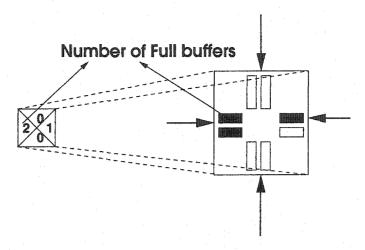

| 4.2  | Representation of full input buffers                             | 62 |

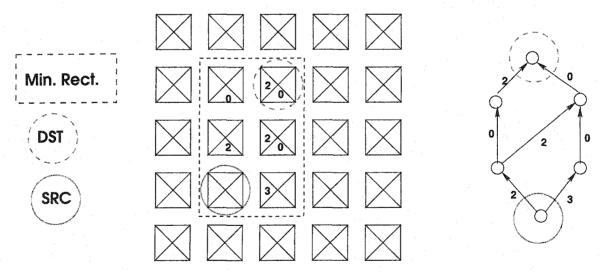

| 4.3  | Recasting <i>LCPmin</i> as SP problem in directed graph          | 62 |

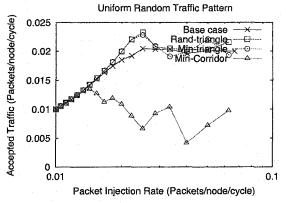

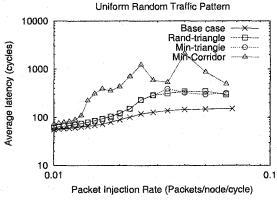

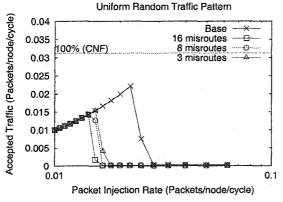

| 4.4  | Via-routing for Uniform Random pattern                           | 66 |

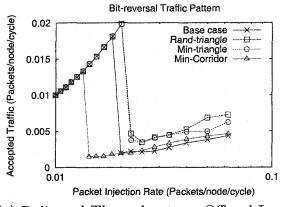

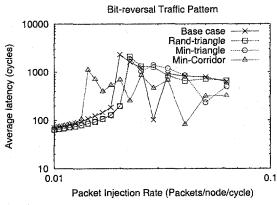

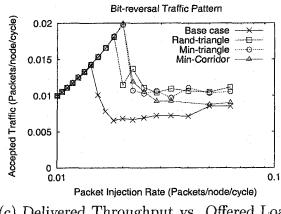

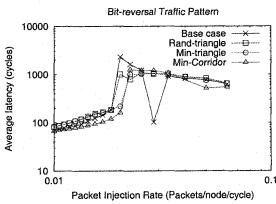

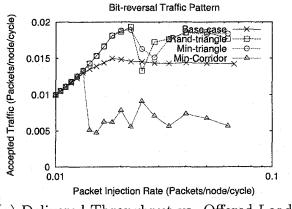

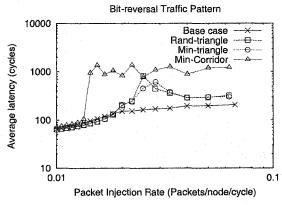

| 4.5  | Via-routing for Bit Reversal pattern                             | 67 |

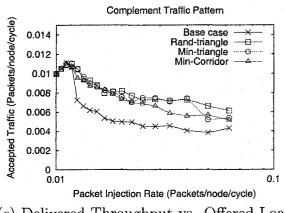

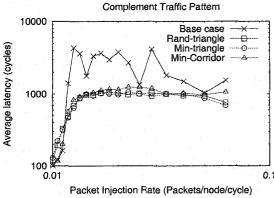

| 4.6  | Via-routing for Complement pattern                               | 68 |

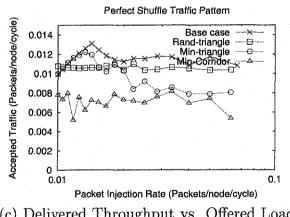

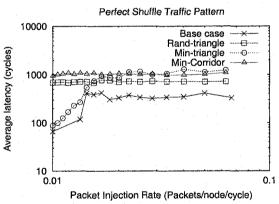

| 4.7  | Via-routing for Perfect Shuffle pattern                          | 69 |

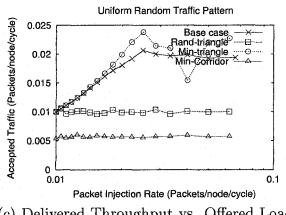

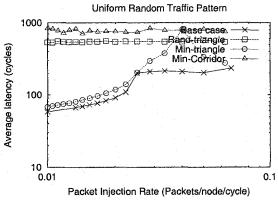

| 4.8  | Via-routing with TUNE for Uniform Random pattern                 | 70 |

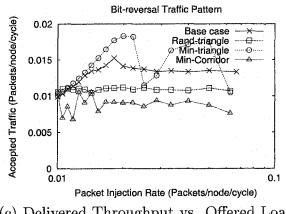

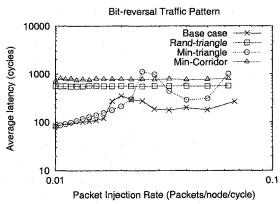

| 4.9  | Via-routing with TUNE for Bit Reversal pattern                   | 71 |

| 4.10 | Via-routing with TUNE for Complement pattern                     | 72 |

| 4.11 | Via-routing with TUNE for Perfect Shuffle pattern                | 73 |

| 5.1  | Minimal Adaptive Routing w/deadlock recovery and Chaotic Routing | 75 |

| 5.2  | Routing Options Minimal vs. Nonminimal                           | 76 |

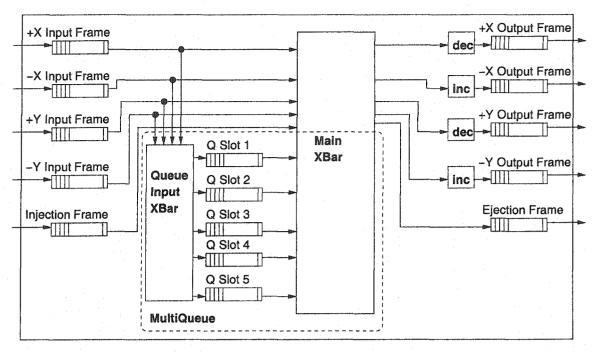

| 5.3  | Central Bypass Buffers: Chaos                                    | 82 |

| 51   | Distributed Bypass Buffers                                       | 84 |

| 5.5  | Choice of Base configuration                                                                 | 88  |

|------|----------------------------------------------------------------------------------------------|-----|

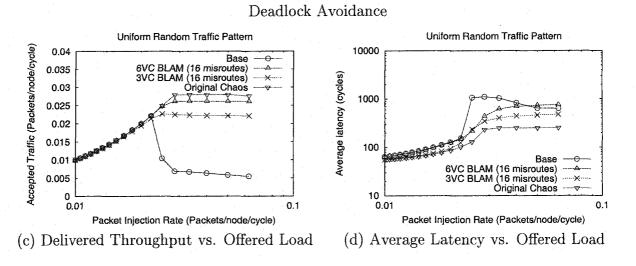

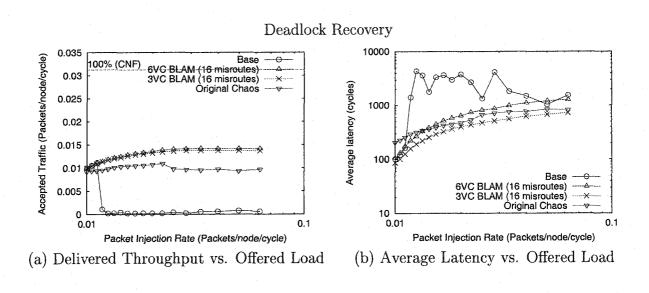

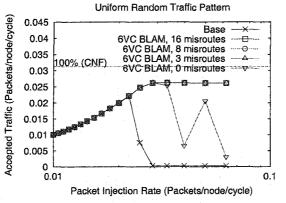

| 5.6  | Overall Performance With Random Traffic                                                      | 94  |

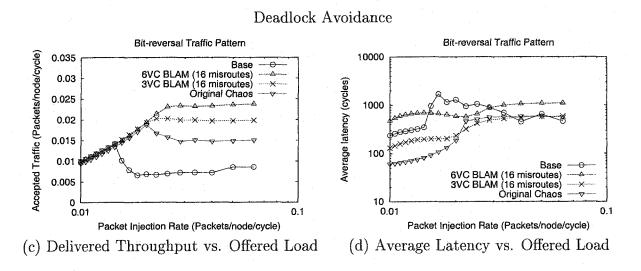

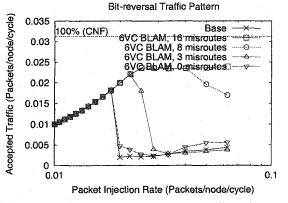

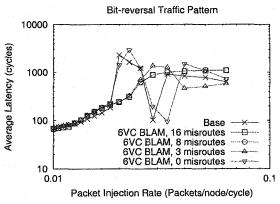

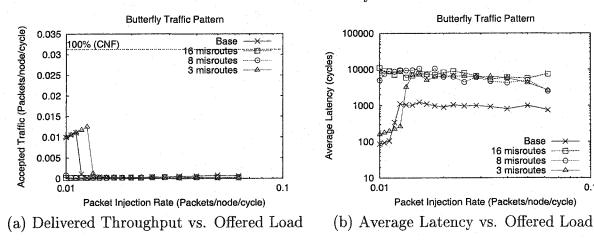

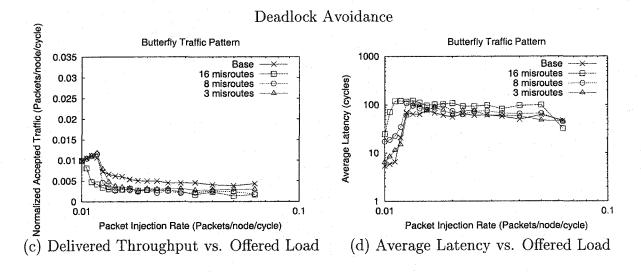

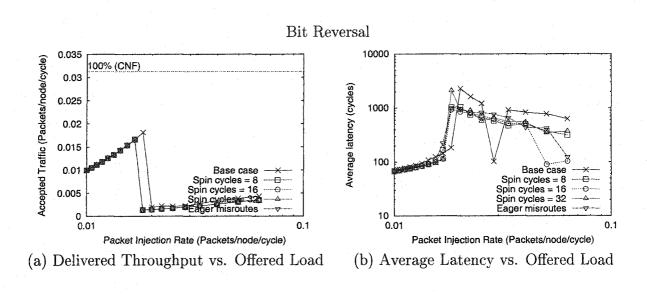

| 5.7  | Overall Performance With Bit-Reversal Traffic Pattern                                        | 95  |

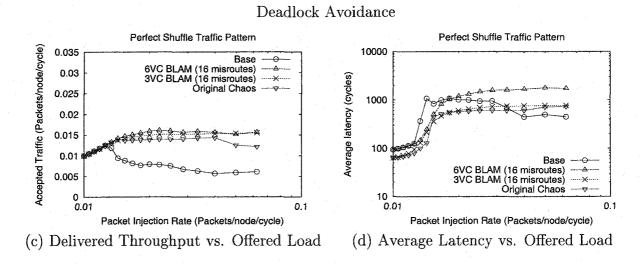

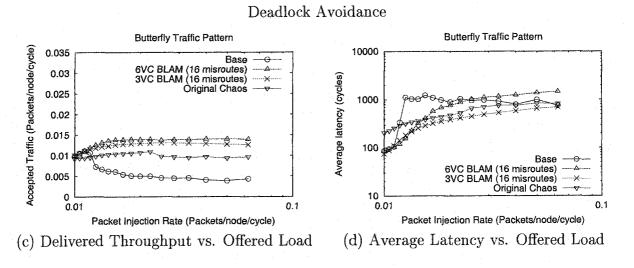

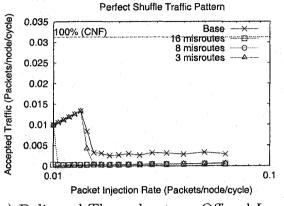

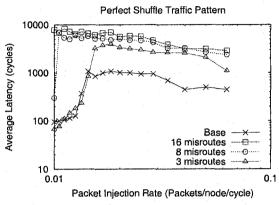

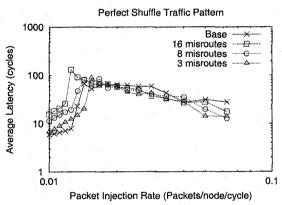

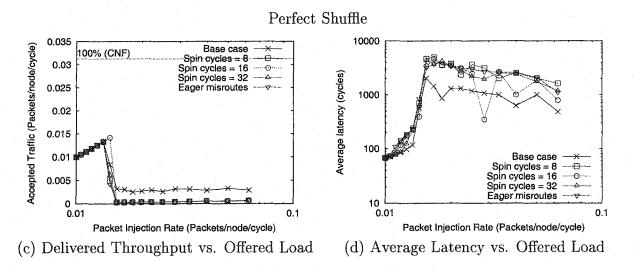

| 5.8  | Overall Performance With Perfect-Shuffle Traffic Pattern                                     | 96  |

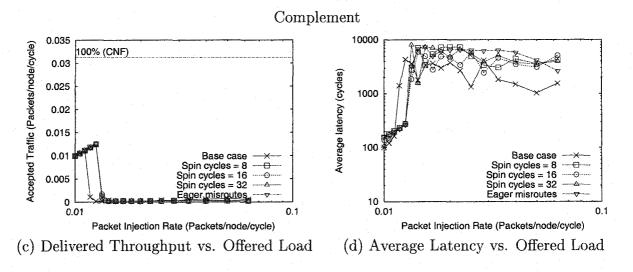

| 5.9  | Overall Performance With Complement Traffic Pattern                                          | 97  |

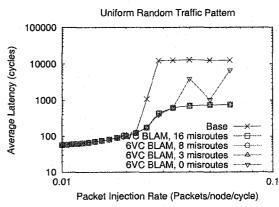

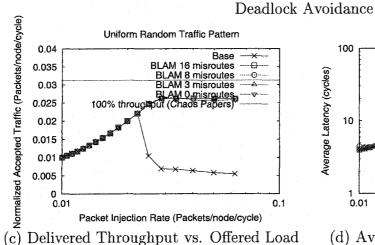

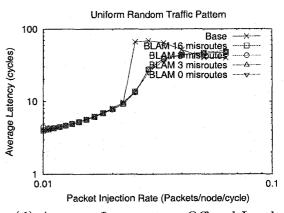

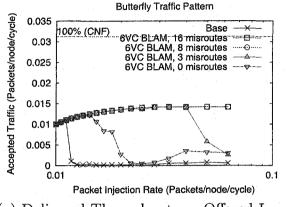

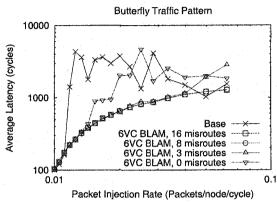

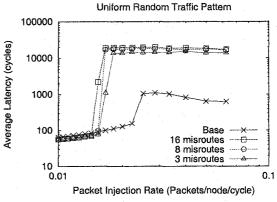

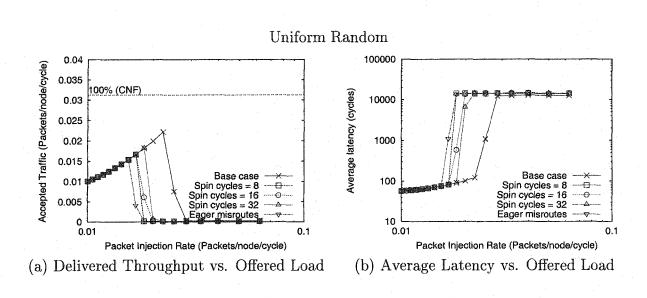

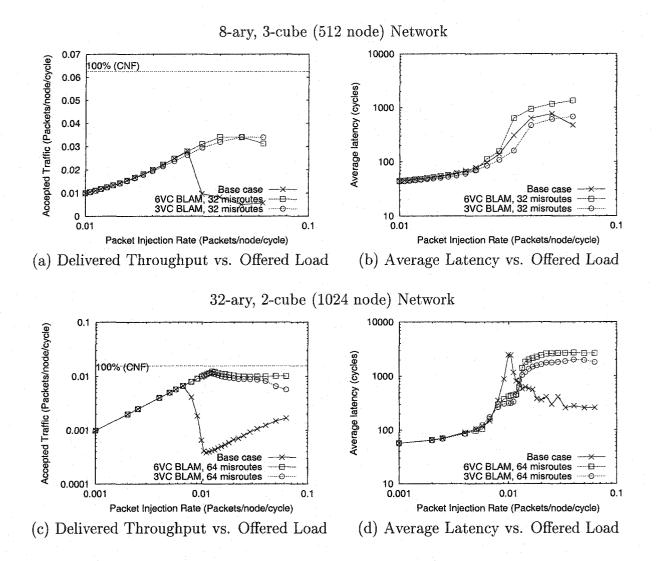

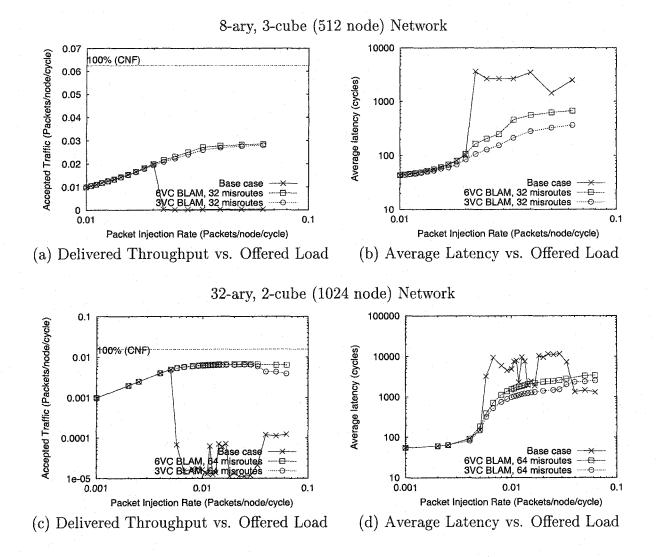

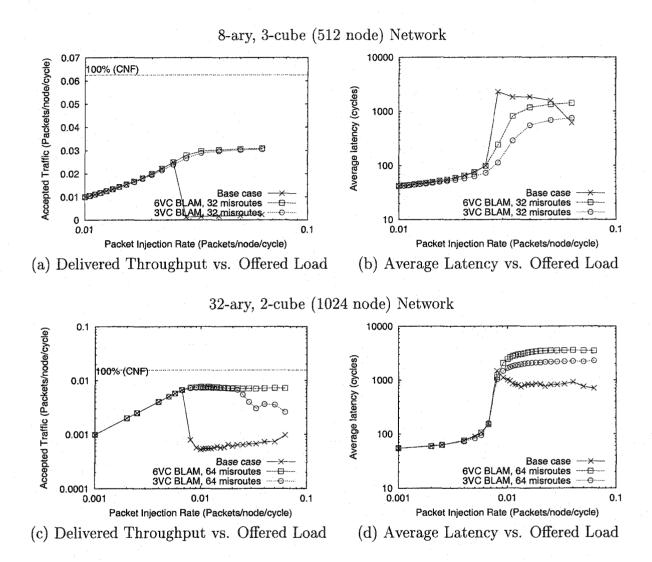

| 5.10 | Effects of Varying the Misroute Limit of BLAM, Uniform Random Traffic                        | 100 |

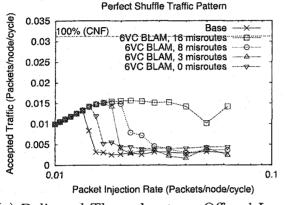

| 5.11 | Effects of Varying the Misroute Limit of BLAM, Perfect Shuffle Traffic                       | 101 |

| 5.12 | Effects of Varying the Misroute Limit of BLAM, Complement Traffic                            | 102 |

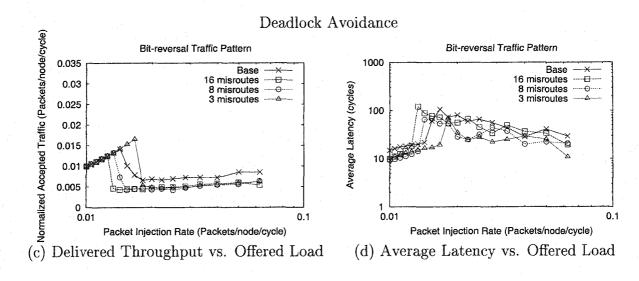

| 5.13 | Effects of Varying the Misroute Limit of BLAM, Bit Reversal Traffic .                        | 103 |

| 5.14 | M-misroute, Adaptive Router, Uniform Random Traffic                                          | 106 |

| 5.15 | M-misroute, Adaptive Router, Perfect Shuffle Traffic                                         | 107 |

| 5.16 | M-misroute, Adaptive Router, Complement Traffic                                              | 108 |

| 5.17 | M-misroute, Adaptive Router, Bit Reversal Traffic                                            | 109 |

| 5.18 | M-misroute, Adaptive Router with lazy Misroutes                                              | 110 |

| 5.19 | M-misroute, Adaptive Router with lazy Misroutes                                              | 111 |

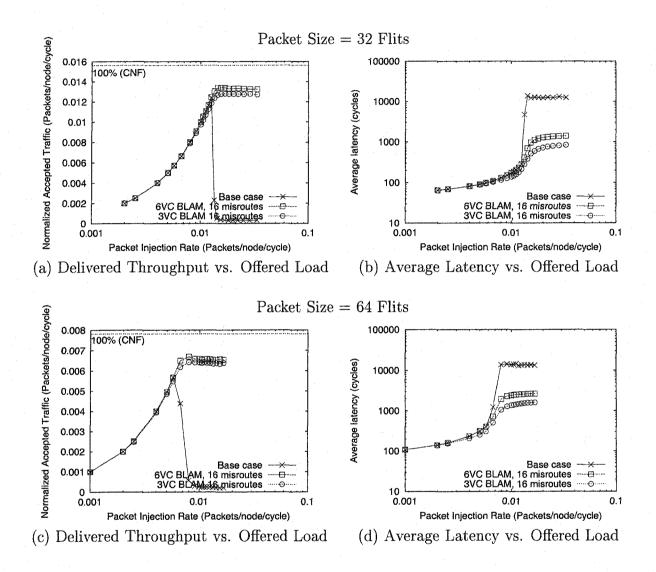

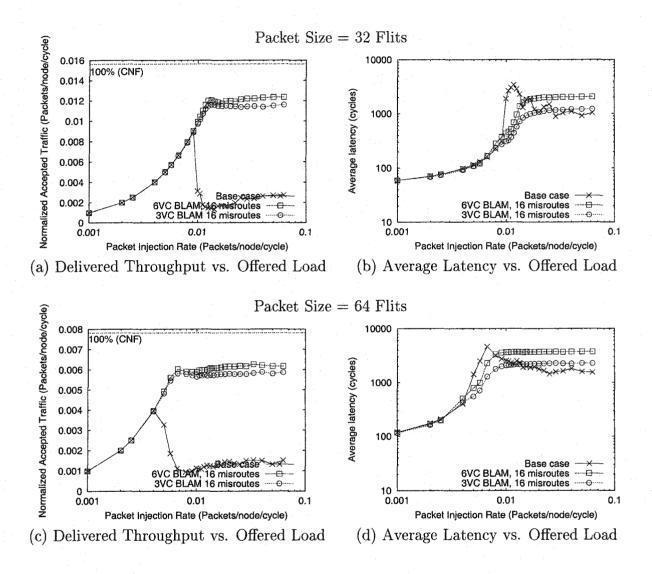

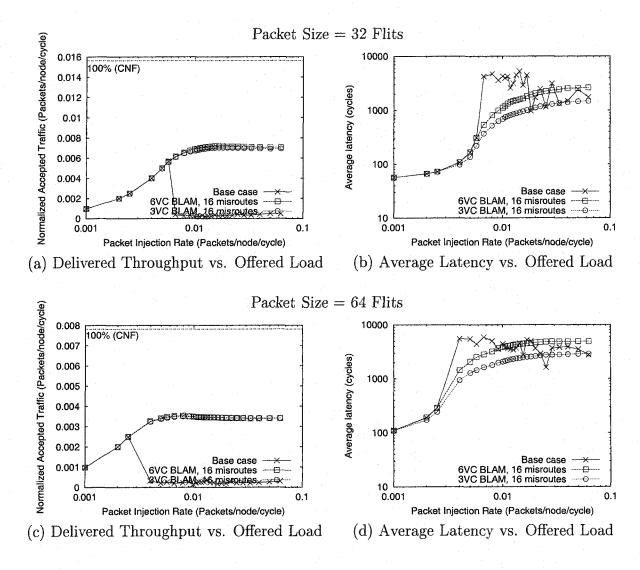

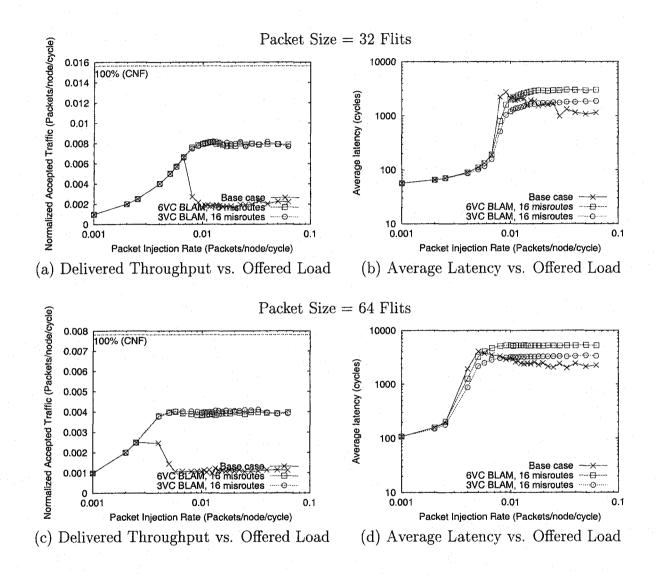

| 5.20 | Overall Performance For Other Packet Sizes (Uniform Random Traffic, 16-ary, 2-cube Network)  | 115 |

| 5.21 | Overall Performance For Other Packet Sizes (Bit-Reversal Traffic, 16-ary, 2-cube Network)    | 116 |

| 5.22 | Overall Performance For Other Packet Sizes (Complement Traffic, 16-ary, 2-cube Network)      | 117 |

| 5.23 | Overall Performance For Other Packet Sizes (Perfect Shuffle Traffic, 16-ary, 2-cube Network) | 118 |

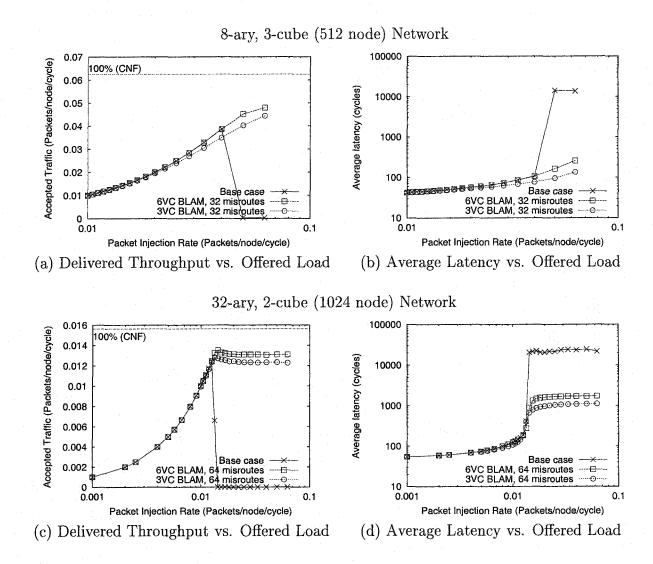

| 5.24 | fic, 16 flit packets)                                                                  | 119 |

|------|----------------------------------------------------------------------------------------|-----|

| 5.25 | Overall Performance For Other Network Sizes (Bit-Reversal Traffic, 16 flit packets)    | 120 |

| 5.26 | Overall Performance For Other Network Sizes (Complement Traffic, 16 flit packets)      | 121 |

| 5.27 | Overall Performance For Other Network Sizes (Perfect Shuffle Traffic, 16 flit packets) | 122 |

#### Acknowledgements

I consider myself lucky to have had Seema by my side these past four years, and I don't think she will ever know how much her love and support has meant to me. I am also extremely thankful to my parents for their love, encouragement and support.

I wish to thank my advisors, Professor Alvin Lebeck and Shubhendu Mukherjee, whose guidance has been extremely valuable to me. The knowledge and experience I have gained under their guidance, both in the methods of research and in specific research insights will help me throughout my career. I would also like to thank members of my PhD examination committee for their suggestions and comments that helped polish my research and thesis.

Working with Professor Siddhartha Chatterjee, Srikanth Srinivasan, Chia-lin Yang and Dave Raymond on my initial research projects as a graduate student was a rewarding and enriching experience. I have also benefited greatly from the many teachers who have taught me at Duke University and IIT Kharagpur.

Finally, it would have been considerably more difficult for me to adjust to my stay far away from India but for the company of all my family and friends. Thank you, Varsha, Babu, Sri, Gopal, Chia-lin, Karthikeyan, Rama, Om, Krishna, Amit, Pavan, Padmini, Kasturirangan, Vamsee, Rajesh, Jaidev, Sphoorthy, Vikram and Rachana for everything.

# Chapter 1: Introduction

The market for large-scale cache-coherent distributed shared-memory multiprocessor machines (DSMPs) with 16 or more processors has tripled in the past four years [9]. In 2001 this server market resulted in an annual revenue of \$9 billion. Roughly half of this revenue resulted from large-scale machines with 32 or more processors. Today most major vendors, such as IBM [12, 22], HP [29, 43, 32], SGI [54], and Sun Microsystems [9], offer machines that scale up to a large number of processors (usually between 24 and 512).

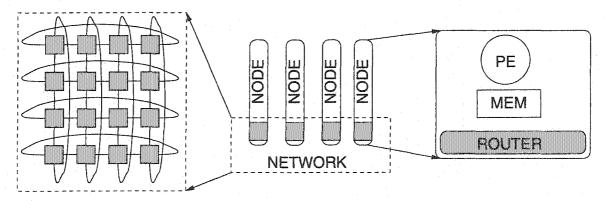

These systems (Figure 1.1) typically consist of a set of *nodes* that can communicate over an *interconnection network*. As shown in Figure 1.1, each node consists of a processing element (PE), memory (including caches) and a router. The interconnection network connects all the routers and allows communication between various nodes.

The memory wall problem in uniprocessor design is useful to illustrate the criticality of interconnection network performance in DSMP performance. In the uniprocessor system context, the growing gap between processor and memory speeds poses a challenge. Memory hierarchies and processor techniques to "tolerate" cache-miss latencies mitigate this problem to an extent, but the gap is too wide to be completely tolerated. This results in processor stalls and reduces overall performance. Consequently, there is a need for high bandwidth and low latency miss servicing to ensure that the processor does not stall waiting for data.

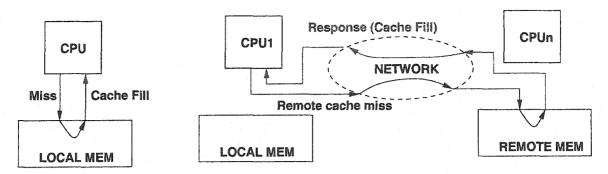

The same problem of miss-service latency and bandwidth is exacerbated in DSMP systems because a cache miss may potentially suffer the interconnection network delay in addition to the memory latency (Figure 1.2). High latencies and/or poor

Figure 1.1: Distributed Shared Memory Systems with k-ary, n-cube networks

bandwidth can increase the time required to service remote cache misses and has the potential to increase processor stall time. As such, high bandwidth, low latency interconnection network performance is desirable in order to achieve high system performance in demanding server applications, such as databases [51]. Further, the advent of multiprocessor systems built with highly aggressive, out-of-order, and speculative microprocessors, simultaneous multithreaded processors [21], and chip multiprocessors [16], promises to dramatically increase the offered load on such multiprocessor networks.

Unfortunately, network packets are often delayed due to transient network congestion. Consequently, many interconnection networks employ virtual cut-through and adaptive routing algorithms. Virtual cut-through pipelines a packet among multiple routers and buffers it entirely at a router when the packet header is blocked due to congestion. This reduces congestion around a router by removing packets from the network links. Adaptive routing routes packets around congested spots in a network (by adapting to the network state) to achieve higher throughput from the network. Virtual channels also help reduce congestion by reducing head-of-line waiting. However, inspite of significant benefits from the use of techniques mentioned above, there remain known performance bottlenecks [48] at high loads due to network saturation.

Figure 1.2: Interconnection network on Critical Path

Tree saturation occurs when multiple packets contend for a single resource (e.g., a link between nodes) creating a hot-spot. Since only one packet can use the resource, other packets must wait. These waiting packets occupy buffers and thus delay other packets, even though they may be destined for a completely different node and share only one link on their paths to their respective destinations. This process continues, waiting packets delay other packets producing a tree of waiting packets that fans out from the original hot-spot.

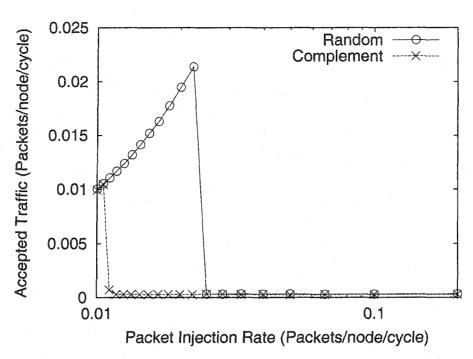

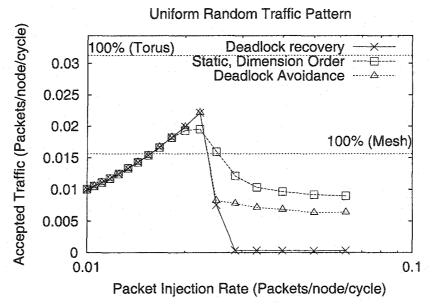

The performance degradation caused by network saturation can be severe, as illustrated in Figure 1.3. The y-axis corresponds to delivered bandwidth (flits/node/cycle) while the x-axis shows offered load in terms of packet injection rate (packets/node/cycle). The two lines correspond to different communication patterns: randomly selecting a destination node (random), and using the node number with its bits inverted as the destination (complement). (I explain communication patterns in greater detail in Section 5.4.3.)

From Figure 1.3 we can make two important observations. First, both communication patterns incur dramatic reductions in throughput when the network reaches saturation. The second observation is that the network saturates at different points for the different communication patterns.

The space of solutions to the problem of performance degradation at network

Figure 1.3: Performance Breakdown at Network Saturation, 16x16 2D network, adaptive routing, deadlock recovery

saturation can be divided into two broad sub-spaces: congestion control mechanisms and load-balancing schemes. The congestion control approach throttles injection of new packets into the network so as to keep the network operating in the high bandwidth, low latency region of operation. This region of operation corresponds to the peak in Figure 1.3 at loads slightly lower than saturation load. The load balancing approach tries to prevent imbalances in load in different regions of the network. The rationale behind this approach is that load imbalances can cause network delays in a small region of the network that can propagate quickly because of the tree-saturation phenomenon.

#### 1.1 Contributions

The contributions of this thesis are the design and evaluation of the following three techniques to achieve high bandwidth, low latency interconnection network operation

Figure 1.4: Minimal Adaptive Routing w/deadlock recovery and Chaotic Routing at high loads. The first technique falls under the congestion control category and the second two techniques fall under the load balancing categories.

• Self-tuned, global knowledge based, congestion control: One way to prevent network saturation is to use source throttling, which prevents source node packet injection when congestion is detected. An oracle could achieve this by knowing both the communication pattern and the packet injection rate that maximizes performance. The challenge is to develop a realistic implementation that can prevent performance degradation at network saturation and adapt to variations in communication patterns.

I propose a self-tuned, global knowledge based congestion control mechanism that achieves both objectives. The two key innovations of this technique are: (a) faster feedback via the use of global congestion information and (b) a throughput driven self-tuned congestion control mechanism that adapts to changes in

communication patterns.

- Congestion-aware via routing: An alternate way would be achieve load balancing by making sure that packets do not flood congested regions of the network. This prevents congestion from building up in regions of the network and thus prevents saturation. I use a mechanism called via-routing that routes packets towards certain intermediate nodes (via nodes) en route to the destination node. The key innovation of my technique is the use of of global knowledge to direct packets to congestion free regions of the network by using global-congestion-aware via-node selection policies.

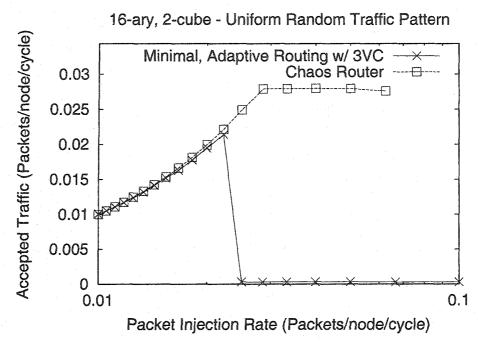

- BLAM routing: Earlier, we had seen the performance bottleneck of minimal adaptive routers, i.e., routers that ensure that packets get closer to the destination with each hop, at high loads due to network saturation. Interestingly, however, non-minimal routing algorithms, which allow packets to take hops that take them farther from the destination, may perform significantly better than a minimal adaptive routing algorithm (Figure 1.4) at high offered loads. This is because non-minimal routing algorithms offer greater routing freedom compared to a minimal adaptive routing algorithms (Figure 1.5.) Figure 1.4 compares the performance of a minimal adaptive router with the Chaos router, which is a non-minimal adaptive router. The minimal adaptive routing algorithm saturates and, thereby, causes the performance to degrade rapidly beyond a certain offered load. Chaos' performance is better on two counts: (a) saturation occurs at higher loads and (b) there is no degradation in performance at saturation. Unfortunately, the better performance of *Chaos* is achieved at the cost of weaker livelock-freedom guarantees. Chaotic routing offers no deterministic guarantee of livelock-freedom—only a probabilistic guarantee that

Figure 1.5: Routing Options Minimal vs. Non-minimal

the chance of a packet continuously circulating in the network diminishes with each hop.

Unfortunately, in spite of its high performance, to the best of my knowledge no commercially available interconnection network uses the Chaos routing algorithm, even though it has been over a decade since the design was proposed. The presence of livelocks-however low its probability may be—causes network designers to shy away from using such algorithms in real products. The challenge is to develop a solution that has the benefits of each of the two routing algorithms (minimal adaptive and Chaos) without either technique's pitfalls. I propose a new non-minimal routing algorithm—BLAM—that has the best features of minimal (deterministic guarantees of deadlock- and livelock-freedom) and non-minimal routing (better performance due to improved flexibility) without the drawbacks of either. The key innovations of this technique are the use of lazy misrouting (to prevent spurious and wasteful misrouting) with bypassing (to eliminate head-of-line waiting) and the use of limited misroutes (to ensure livelock-freedom).

#### 1.2 Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 provides background information and discusses related work. The next three chapters describe and evaluate three techniques to achieve high bandwidth low latency network operation in interconnection networks. Chapter 3 describes a congestion control mechanism that relies on global information for faster feedback and self-tuning for adapting to various communication patterns. Chapter 4 proposes a mechanism for congestion aware viarouting that attempts load balancing to overcome the performance problems at high loads. Chapter 5 describes a new high performance non-minimal routing algorithm—BLAM—that is guaranteed to be livelock- and deadlock-free. Chapter 6 summarizes and concludes this thesis.

#### Chapter 2:

#### Background and Related Work

#### 2.1 Background

High performance interconnection networks in tightly coupled multiprocessors can be achieved by using wormhole [14, 15] or virtual cut-through switching [35], adaptive routing [28], and multiple virtual channels [13]. Many commercial machines [43, 53, 39] use a combination of these techniques for their interconnection networks. In these systems communication occurs by sending packets of information that are routed independently through the network. Each packet is composed of flits (flow control units) that are transferred between network nodes. Usually, the header flit(s) contains information necessary to choose a route to the destination.

In wormhole switching, when a node receives the header flit (which typically contains the routing information), it immediately selects a route and forwards the flit to the next node. This can provide very low latency compared to store-and-forward routing where the entire packet is received by a node before forwarding it. However, when a packet blocks in a wormhole network, its flits occupy buffer space across several network nodes. In contrast, virtual cut-through routers can buffer the entire blocked packet within a single node while also providing low latency at light loads, since they forward packet headers without waiting for the whole packet to arrive.

In the rest of this section, I describe the network topology and the router architecture I consider in this thesis.

<sup>&</sup>lt;sup>1</sup>For ease of exposition I assume each network node contains a processor, memory and a network router.

#### 2.1.1 Network Topology

In this thesis, I consider *direct* networks of the k-ary, n-cube topology. Direct networks are networks where each node can produce/consume network packets (i.e. each node has a processor and memory). In contrast, *indirect* networks may have intermediate switches which relay other packets but do not produce/consume any traffic.

One attractive property of indirect networks is that the node containing the processor can use all the available pin bandwidth exclusively for its communication needs. In an integrated direct network, part of the node's pin bandwidth may be used to relay packets of two other nodes in the system. However, this thesis does not consider indirect networks (such as fat-trees, multistage interconnection networks) for two reasons: (1) The trend towards higher integration and system-on-a-chip is leading towards direct networks since the processor, caches and router can all be integrated on one die, (2) Indirect networks can be modeled with direct networks where certain hosts do not produce/consume any traffic, essentially acting as intermediate switches.

Of the various possible topologies among direct networks, this thesis considers the k-ary, n-cube topology (which is an n-dimensional matrix with k nodes along each dimension and wrap-around edges) because it has many desirable properties. k-ary, n-cube networks have a large number of alternate routes between a source and a destination. k-ary, n-cube topologies are a broad family that include many popular topologies such as rings (k-ary, 1-cube), meshes (k-ary, 2-cube with some routing restrictions) and hypercubes (2-ary, n-cube).

#### 2.1.2 Base Router Architecture

Above, I described the network architecture. Here I discuss the architecture of each router in the network. Figure 2.1 shows the *minimal*, *adaptive* router with *multiple*

Figure 2.1: Base Minimal, Adaptive Router with Multiple Virtual Channels

virtual channels that I use as the base case router in the rest of this thesis. The next few paragraphs describe each of these characteristics of my base router in greater detail.

Each node has several incoming and outgoing network physical links and injection/ejection channels through which packets enter/exit the network. The physical channels are logically split into multiple virtual channels, each with its own buffers. The routing and arbitration unit sets up the crossbar connections linking input buffers to output buffers. Flits deposited in the output buffer are transferred across the physical link into the corresponding input buffer at the neighboring node.

A packet hop is classified as *profitable* or *minimal* if it takes the packet closer to its destination. A hop that takes a packet farther from its destination is known as a *misroute* or a *non-minimal hop*. A *profitable channel* is a channel on which a packet can make a profitable hop. We can classify routers as minimal or non-minimal. A minimal router offers only profitable hops whereas a non-minimal router may offer misrouting hops as well.

Adaptive routing dynamically chooses from multiple potential routes based on current local network state. This offers more routing flexibility compared to a deterministic routing algorithm, and thus provides higher performance. Unfortunately, full adaptive routing can cause deadlock cycles. The next section describes ways to handle deadlock cycles that form due to adaptive routing.

#### 2.1.3 Deadlock Handling in Minimal Adaptive Routers with Escape Paths

Virtual channels allow multiple packets to share a single physical link and can be used to eliminate deadlocks. Deadlock avoidance schemes work by preventing the cyclic dependencies between storage resources. In particular, I consider a scheme that reserves a small set of virtual channels for deadlock-free routing [18], while the remaining virtual channels use fully adaptive routing. This technique guarantees forward progress, since packets routed over the special channels will never deadlock, and eventually free up resources for the fully adaptive channels. The Alpha 21364 router [43] is an example of a system with multiple virtual channels, adaptive routing and deadlock avoidance.

Deadlock recovery [38] is an alternative to deadlock avoidance that can potentially achieve higher performance. Deadlock recovery uses full adaptive routing on all virtual channels, detects when deadlocks occur (typically via timeouts), then recovers by routing packets on a deadlock-free path which uses a central per-node buffer. This is the primary difference from deadlock avoidance, which requires buffers per physical channel.

In either deadlock avoidance or recovery, the frequency of deadlocks in the adaptive channels increases dramatically when the network reaches saturation [38]. When this occurs, packets are delivered over the relatively limited escape bandwidth available on the deadlock-free paths. This causes a sudden, severe drop in throughput

and corresponding increase in packet latency.

#### 2.2 Related Work

The contribution of this thesis is the design and evaluation of three techniques to overcome the problem of performance degradation at saturation and to sustain high-bandwidth, low latency network operation. In this section, I discuss previous research and its relation to the three techniques. Section 2.2.1 describes various research studies that used the congestion control techniques and compares it with my technique described in Chapter 3. Section 2.2.2 describes previous load-balancing research and its relation to my congestion aware via-routing technique described in Chapter 4. Finally, Section 2.2.3 describes the livelock, deadlock and performance issues that crop up when non-minimal routing is considered. This provides the background for Chapter 5 where I describe and evaluate a non-minimal routing algorithm—BLAM.

#### 2.2.1 Congestion Control

Most previous work on congestion control for multiprocessor networks relies on estimating network congestion independently at each node and limiting packet injection when the network is predicted to be near saturation. This reduces the problem to finding a local heuristic at each node to estimate network congestion. Lopez et al. [40, 41] use the number of busy output virtual channels in a node to estimate congestion. Baydal et al. [4] propose an approach that counts a subset (free and useful) of virtual channel buffers to decide whether to throttle or not. Because the above schemes rely on local symptoms of congestion, they lack knowledge about the global network state, and are unable to take corrective action in a timely manner. This reduces their effectiveness under different network load levels and communication patterns.

Smai and Thorelli describe a form of global congestion control [56]. A node that detects congestion (based on time-outs) signals all the other nodes in the network to also limit packet injection. This approach requires tuning the appropriate time-outs, and when the timeouts are tuned for robustness at higher loads, there is a performance penalty for light loads. Scott and Sohi describe the use of explicit feedback to inform nodes when tree-saturation is imminent in multistage interconnection networks [52]. This approach also requires tuning of thresholds. The technique proposed by Kim et al. [36] allows the sender to kill any packet that has experienced more delays than a threshold. This approach pads shorter packets to ensure that the sender can kill a packet at any time before its first flit reaches the destination. This can cause larger overheads when short messages are sent to distant nodes.

The above techniques for congestion control in multiprocessor networks all attempt to prevent network saturation at heavy loads. Unfortunately, these techniques either require tuning, lack necessary information about a network's global state to take preventive actions in a timely fashion, or do not provide high performance under all traffic patterns and offered load levels.

Flit-reservation flow control is an alternative flow control technique which improves the network utilization at which saturation occurs [47]. It uses control flits to schedule bandwidth and buffers ahead of the arrival of data-flits. This pre-scheduling results in better re-use of buffers than waiting for feedback from neighboring nodes to free up buffers. Basak and Panda demonstrate that consumption channels can be a bottleneck that can exacerbate tree saturation. They show that saturation bandwidth can be increased by having an appropriate number of consumption channels [3].

LANs (Local Area Networks) and WANs (Wide Area Networks) use self-tuned congestion control techniques. Various flavors of self-tuning, end-to-end congestion avoidance and control techniques have been used in the TCP protocol [33, 6]. TCP's

congestion control mechanism uses time-outs and dropped/unacknowledged packets to locally estimate global congestion and throughput. If congestion is detected, the size of the sliding window, which controls the number of unacknowledged packets that can be in flight, is reduced. Floyd and Jacobson [26] proposed a scheme where TCP packets are dropped when a router feels that congestion is imminent. Dropped packets give an early indication to end hosts to take corrective action and scale back offered load. Floyd [25] also proposed a modification of TCP where "choke packets" are explicitly sent to other hosts. Ramakrishnan and Jain describe a similar mechanism for DECbit to explicitly notify congestion whereby gateways set the ECN (Explicit Congestion Notification) bit depending on average queue size [50].

Congestion control in ATM [34] uses explicit packets called Resource Management (RM) cells to propagate congestion information. Switches along the packet path modify bits in the RM cells to indicate the highest data rate they can handle. The end-hosts are limited to using the maximum data-rate indicated by the switches to not overwhelm the network and/or switches.

Congestion control mechanisms for LANs and WANs that involve dropping packets are not directly applicable in multiprocessor networks. Some LANs and WANs can drop packets because higher network layers will retransmit dropped packets for reliable communication. The dropped packets serve as implicit hints of network congestion. However, multiprocessor networks are typically expected to guarantee reliable communication. Thus, additional complexity would have to be built-in to store and retransmit dropped packets. The alternative idea of propagating congestion information explicitly can be used.

The challenge is in determining the appropriate set of mechanisms and policies required to provide a self-tuned congestion control implementation for preventing saturation in multiprocessor networks. In Chapter 3, I present my solution for regu-

lar interconnection networks with adaptive routing, wormhole switching, and either deadlock recovery or deadlock avoidance.

My solution—Tune—is based on two key innovations that collectively overcome the limitations of previous congestion control techniques. First, I use a global knowledge based congestion estimation that enables a more timely estimate of network congestion. The second component is a self-tuning mechanism that automatically determines when saturation occurs allowing throttling packet injection. Chapter 3 describes and evaluates the Tune congestion control mechanism.

#### 2.2.2 Load Balancing in the Minimum Rectangle

Load balancing schemes generally try to distribute packets evenly over the network. One mechanism that has been widely studied to achieve this is to require packets to traverse certain intermediate nodes on the way to their respective destination nodes. With such a mechanism, the problem of balancing load reduces to selecting intermediate nodes evenly over the network. The mechanism of requiring packets to traverse intermediate nodes is also called *multi-phase routing*.

Valiant [64] proposed a two-phase routing scheme that randomly selected a single via-node that was not necessarily in the minimum rectangle. While this approach guarantees balanced loads and good worst case behavior, it effectively doubles the expected path-length for each packet. Nesson et al. [44] describe a non-adaptive routing technique called ROMM routing which uses multiphase-routing by selecting random via-nodes in the minimum rectangle, but their scheme requires twice as many virtual channels as phases to achieve deadlock-free routing in a torus. Towles and Dally [62] demonstrate that the worst case behavior of ROMM routing is poorer than that of static dimension-ordered routing.

The Randomized Load Balancing (RLB) algorithm by Singh et al [55] uses two

levels of load balancing. It uses quadrant selection to balance global link loads. This results in non-minimal routing as well. It uses 2-phase routing within the selected quadrant to balance load locally. This scheme is not adaptive and further, it penalizes performance on well-behaved traffic patterns though it improves the performance for adversarial communication patterns.

Overlay networks [1] on top of the Internet achieve better performance through load balancing and fault tolerance by routing packets via overlay nodes that would not normally be on the path if the underlying Internet mechanism had routed the packet. Resilient overlay networks [2] use fast feedback to detect heavily loaded network regions (as indicated by packet loss rates) faster than the underlying Internet infrastructure and hence are able to direct packets over lightly loaded networks in a timely manner. However, in overlay networks on the Internet, the problem is not only because of slower feedback, but also because the underlying Border Gateway Protocol (BGP) deliberately exposes less information than it has. This is done to achieve scalability. In contrast, in distributed, shared memory multiprocessor networks with adaptive routing, there is no such artificial restriction on routing freedom. But lack of fast feedback can still result in load imbalances and consequent performance degradation.

The Source Demand Routing Protocol (SDRP) is an Internet protocol that lets source nodes specify the inter-domain hops of packets. However, the imperentation of SDRP depends on deployment of SDRP-capable routers. In the absence of SDRP routers, routing defaults to ordinary hop-by-hop routing as in Border Gateway Protocol(BGP) and Internet Domain Routing Protocol (IDRP). A version of SDRP for IPv6 called Explicit Routing Protocol (ERP) is also in the works.

For local area networks, Flich et al. [24] propose a scheme to select via nodes, to achieve shortest path routing in up\*/down\* routed irregular networks such as

Myrinet. This technique of breaking a route into sub-routes retains deadlock-freedom and achieves shortest paths.

The key innovations of my congestion-aware via-routing scheme, which is described and evaluated in greater detail in Chapter 4, is the use of global information to achieve centralized adaptive routing within the minimum rectangle. The goal is to use global buffer occupancy information and specify, at the source node, that packets move away from heavily loaded network regions. This is different from distributed adaptive routing in which adaptive routing decisions are made at each hop to achieve local load balance. Simulation results show the limitations of load balancing within the minimum rectangle and thus gives the necessary insight for achieving better performance with a new non-minimal routing algorithm—BLAM.

#### 2.2.3 Deadlock, Livelock and Performance Issues in Nonminimal Adaptive Routers

Adaptive routing systems (including out base minimal adaptive router) may be prone to deadlocks. Previously I discussed one approach to handling deadlocks in adaptive channels: guarantee that packets are able to make forward progress on a logically separate subnetwork. Deadlock avoidance [18] and deadlock recovery [38] are examples of this approach. Below, I discuss a different approach to deadlock handling in non-minimal adaptive routers that differs in its performance under heavy load and in its livelock-freedom guarantees.

Deflection routing is another class of routing algorithms that avoid deadlocks in virtual cut-through networks by ensuring that no packets are blocked indefinitely. This technique works for networks where the number of input network channels is equal to the number of output channels at each node. This property makes it possible to match every incoming packet to an output channel. However, such a matching

cannot guarantee that all matched pairs correspond to profitable routes. In fact, using this approach to prevent deadlocks requires an unlimited number of misroutes. This approach eliminates the need for deadlock-free escape paths, but guarantees of livelock freedom are either weaker (probabilistic) or they come at the cost of added complexity to implement timestamping and router-wide priorities.

Synchronous deflection routers [23, 31, 42, 57, 58] assume that all packets arrive at an input port at the same time and they are routed to the output ports in a single step. Non-synchronous routers use the same principle of deflection routing but relax the constraint of synchronous operation by adding buffers that can hold incoming packets while waiting for output channels to become free [45, 37]. Such routers need additional mechanisms like the packet exchange protocol [45] to prevent deadlocks. This protocol demands that if a node a sends a packet on a link to a neighboring node b, node a should also be prepared to accept a packet from node b. The Chaos router [37] belongs to this category. Ngai et al. [45] and Coates et al. [11] describe other examples of non-synchronous deflection routers.

Ngai et al. propose a timestamp based technique to eliminate livelocks, by ensuring that the oldest packet in the network is never misrouted. This guarantees deterministic livelock freedom but the implementation of router-wide priorities (e.g. finding "oldest" packet at the router) can complicate the router and add overheads. The S-connect interconnect of the S3.mp system is another example of a non-synchronous deflection router [46]. Incoming packets that cannot be mapped to channels indicated by the routing table may be routed on any random channel. S-connect also uses an implementation of timestamping and router-wide priorities to guarantee livelock freedom.

I use the *Chaos* router [37] as a representative of non-synchronous deflection routing algorithms as it compares very well against previous deflection routers. The *Chaos*

router does not provide deterministic guarantees of livelock-freedom, thus eliminating the need to implement router-wide priorities. Instead, it uses randomization to select packets to misroute causing the probability of a packet remaining undelivered to diminish with time.

In the above discussion, I outlined a design space of routers with minimal adaptive routers — which disallow misroutes and thus eliminate livelocks — on one end, and chaotic routing — which achieves high performance and deadlock freedom by allowing unlimited, lazy misroutes but offers only probabilistic guarantees of livelock-freedom — on the other end. In the Chapter 5, I analyze this design space of routers with respect to network performance, livelock-freedom and deadlock-freedom guarantees. This analysis provides the insight necessary to develop a routing algorithm—BLAM—that has the best features of both classes of routers. Compared to the congestion control approach, BLAM offers an additional advantage as it increases the applied load at which saturation occurs and avoids throughput degradation at saturation without placing limits on packet injection beyond those imposed by simple back-pressure.

#### Chapter 3:

# Tune: A Self-tuned Congestion Control Mechanism

This chapter presents a self-tuned, global information based, congestion control mechanism—*Tune*—for k-ary, n-cube interconnection networks. In general, congestion control techniques work by throttling packets at the source when they detect that saturation is imminent.

One key innovation of *Tune* is the use of global information that takes distant network conditions into account. Global information enables detection of distant network congestion earlier than alternative approaches described in previous studies (Section 2.2.1) that wait for network backpressure to create locally observable indicators of congestion (e.g., local buffer occupancy, timeouts). *Tune* uses global knowledge of the number of full network buffers to estimate network congestion. This global buffer occupancy is compared against a "threshold" to control packet injection. If it is higher than the threshold, packet injection is stopped. When the buffer occupancy drops below the threshold, packet injection is resumed.

The second key aspect of the *Tune* source throttling scheme is a self-tuning mechanism that monitors network throughput and automatically determines the appropriate threshold value. This eliminates manual tuning and allows my scheme to adjust to variations in communication patterns.

I believe that my congestion control mechanism is generally applicable to a broad range of packet-switched, multiprocessor networks, including virtual cut-through [35] networks and wormhole networks [15, 14]. However, in this thesis, I evaluate the technique in the context of wormhole switched, k-ary, n-cube networks.

Simulation results for a 16-ary, 2-cube (256 node network) show that the Tune

congestion control technique prevents the severe performance degradation caused by network saturation. By limiting packet injection, my scheme sustains high throughput and low latency. Compared to an alternative approach that uses local estimates of congestion [4], *Tune* is superior because global congestion estimation enables it to detect congestion in its early stages. I also show that a single static threshold cannot accommodate all communication patterns because a single threshold overthrottles some workloads and does not prevent saturation in other ones. In contrast, simulations reveal that my self-tuning technique automatically adapts to various communication patterns, including bursts of different patterns.

Section 3.1 and Section 3.2 discuss the two key innovations of this chapter. Section 3.1 presents the proposed global information gathering scheme and Section 3.2 describes the self-tuned congestion control scheme. Section 3.3 and Section 3.4 present the experimental methodology and simulation results, respectively. Section 3.5 summarizes this chapter.

#### 3.1 Gathering global information

Any congestion control implementation requires a timely way to detect network congestion. Previous techniques estimate network congestion using a locally observable quantity (e.g., local virtual buffer occupancy, packet timeouts). While these estimates are correlated to network congestion, waiting for local symptoms of network congestion is less useful primarily because, by that time, the network is already overloaded.

Consider the case when network congestion develops at some distance from a given node. Schemes that use local heuristics to estimate congestion rely on back-pressure to propagate symptoms of congestion to the node (e.g. filling up of buffers, increase in queue delays, etc.). The node takes no corrective action until congestion

symptoms are observed locally.

It is possible to detect network congestion in its early stages by taking global conditions into account. To achieve this, I use the fraction of full virtual channel buffers of all nodes in the network as the metric to estimate network congestion. This ensures that far away congestion is accounted for early enough to take corrective action. However, there is additional cost, both hardware and latency, to propagate the global information.

Tune counts full buffers to estimate congestion but does not take the distribution of these full buffers among the nodes into account. At first glance, this appears to be a serious limitation because it is unable to distinguish between a case with localized congestion (i.e., a large fraction of full buffers are in relatively few nodes in the network) and a benign case (in which the same number of full buffers are distributed more or less evenly among all the nodes of the network). But the adaptivity of Tune's self-tuning mechanism reduces the impact of this problem by setting the threshold differently in the two cases. Tune will set a higher threshold for the benign case than for the case with localized congestion.

In the next section, I show how global information can be gathered with reasonable cost and used to achieve a robust, self-tuned congestion control implementation.

### 3.1.1 Implementing Global Information Gather

Tune requires that every node in the network be aware of the aggregate number of full buffers and throughput for the entire network. (The relationship between full buffers, offered load and delivered bandwidth is explained in Section 3.2.) There are a variety of ways to implement this all-to-all communication. In this section, I study two alternatives: meta-packets, and a dedicated side-band.

One approach to distribute information is to send out special meta-packets con-

taining the congestion and throughput information. The required all-to-all communication can be guaranteed by this approach. However, guaranteeing delay bounds involves additional complexity. Meta packets flooding the network will also consume some of the bandwidth and may add to the congestion. Adding a high-priority virtual channel reserved for these meta-packets is one way of addressing these concerns. My experiments show that even the addition of a high-priority virtual channel is not sufficient to ensure timely information distribution for the purpose of congestion control. I discuss the meta packet mechanism in Section 3.4.5 in greater detail.

For the rest of this chapter, I use an exclusive side-band reserved for communicating the congestion and throughput information. This is the costliest implementation in terms of additional hardware and complexity. However, it is easy to guarantee delay bounds on all-to-all communication and it does not affect performance of the main data network. While the extra bandwidth available on the side-band could be used for general packet routing, it will only postpone network saturation for a short time, and not provide a complete solution like my congestion control scheme.

Apart from meta packets and side-bands, it may be possible to piggy-back the extra information on normal packets and use this as an information distribution mechanism. However, this approach has the disadvantage that it is difficult to guarantee all-to-all communication. Since only nodes involved in communication see the piggy-backed information, it is possible that some nodes will not see the information for an extended period of time, if at all. As such, I do not consider this information distribution mechanism in this thesis.

To compute the global buffer occupancy using the exclusive side-band, I use a dimension-wise aggregation scheme. Assume the side-band incurs a neighbor-to-neighbor communication delay of h cycles. Every node communicates its number of full buffers and throughput in both directions along the lowest dimension of the

Figure 3.1: Dimension-wise global aggregation.

network. Each node that receives such information computes the aggregate and has the aggregate information for all its neighbors along the zeroth dimension at the end of k/2 hops or (k/2) \* h cycles. The nodes then communicate the aggregates to neighbors along the next higher dimension. Continuing this procedure along every dimension, global aggregation in a full-duplex, k-ary,n-cube network completes in (k/2) \* h \* n cycles. Assuming h = 2, for the 16-ary, 2-cube network configuration (n = 2, k = 16) it takes 32 cycles. I refer to the time for such an all-to-all communication as the gather-duration (g).

The mechanism described above provides g-cycle delayed snapshots of the network congestion every g cycles. Tune's congestion control policy requires a comparison, in every cycle, between the current estimated congestion to the threshold. If the system is currently at time t and the previously observed network snapshots have been observed at  $S_2$ ,  $S_1$ ,  $S_0$  and so on, Tune must estimate the network congestion at time t based on the previous snap-shots of global network congestion.

The simplest solution is to use the state observed in the immediately previous

Figure 3.2: Estimation of global congestion: Previous Snapshot vs. Linear Extrapolation.

network snapshot until the next snapshot becomes available. I use a linear extrapolation based on the previous two network-snapshots as an estimate of congestion. In general, any prediction mechanism based on previously observed network states can be used to predict network congestion. On average, I found the linear extrapolation technique yields an improvement in throughput of 3% for the deadlock avoidance configuration and 5% for the deadlock recovery configuration over using the state seen in previous network snapshot.

To communicate congestion information, nodes exchange full buffer counts. The number of bits needed to represent this information depends on the number of buffers in the network. The network configuration I use and the number of bits needed to represent congestion information for that configuration is specified in Section 3.3.

In summary, global measurement of virtual buffer occupancy provides an early estimate of network congestion. This estimate is compared against a threshold to determine if packet injection should stop or resume. Obtaining information on the global state of the network is only part of the solution. To translate this congestion estimate to good congestion control, *Tune* has to properly choose the threshold.

Tune's self-tuning mechanism, described in the next section, dynamically tunes the threshold to the appropriate values.

## 3.2 Self-Tuning Mechanism

Proper threshold selection is a crucial component of my congestion control implementation. Inappropriate threshold values can produce unstable behavior at high loads or unnecessarily limit performance for light loads. Furthermore, there is no single threshold that works well for all communication patterns. This section presents a technique to automatically determine the proper threshold value.

The goal of *Tune*'s self-tuning mechanism is to maximize delivered throughput without dramatic increases in packet latency. Therefore, we can view the task as an optimization problem with delivered bandwidth as an objective function dependent on the number of full virtual buffers. Consider the relationship between offered load, full buffers and delivered bandwidth (See Figure 3.3). As offered load increases from zero, the number of full virtual buffers and delivered bandwidth also increase. When saturation occurs, the delivered bandwidth decreases while the number of full virtual buffers continues to increase.

Tune's self-tuning technique is attempting to find the number of full virtual buffers (i.e., the threshold value) that maximizes delivered throughput (B in Figure 3.3). To achieve this, Tune uses a hill-climbing algorithm including a technique to avoid local maxima. It is possible obtain a measure of global network throughput (the objective function) in a manner similar to the way Tune obtains the global count of full virtual buffers (see Section 3.1.1). Nodes exchange the number of flits delivered in the past g cycles to measure throughput. Since the maximum possible delivered bandwidth is 1 flit/node/cycle, the count will not exceed g\*NodeCount.

Figure 3.3: Throughput vs. Full Buffers

#### 3.2.1 Hill Climbing

To automatically tune the threshold, *Tune* begins with an initial value based on network parameters (e.g., 1% of all buffers). Using intuition about the relationship between the number of full buffers and delivered bandwidth, I specify a tuning decision table that indicates when the threshold value must be increased or decreased. Too low a value (A or lower in Figure 3.3) prevents the network from reaching the peak by over throttling packet injection. In contrast, too high a value pushes the network beyond the peak (C or higher in Figure 3.3), causing saturation just like a network without any congestion control.

A discussion of *Tune*'s hill-climbing component of its self-tuning mechanism will have to answer the following questions.

• How often does Tune alter this estimate? It uses a very simple scheme in which it updates the estimate at a constant frequency. The tuning period is an

| Drop in Bandwidth $> 25\%$ ? | Currently Throttling? |           |

|------------------------------|-----------------------|-----------|

|                              | Yes                   | No        |

| Yes                          | Decrement             | Decrement |

| No                           | Increment             | No Change |

Table 3.1: Tuning decision table

exact multiple of the gather-duration. If the tuning period is very large, there is likely to be slow and inefficient tuning leading to network underutilization or network saturation. If it is too small, short-lived crests and troughs in throughput could alter the estimate. However, in my experiments, I found that, for a reasonable range of values (32 cycles to 192 cycles) the performance did not alter significantly. In most experiments, I use a 96 cycle tuning period.

- What policy determines whether the tuning mechanism should increment or decrement the estimate? Tune uses the policy outlined in Table 3.1. The two dimensions in the table correspond to observed network throughput and whether or not the network is currently throttled. A tuning decision is made once every tuning period. A "drop-in-throughput" is said to occur when the throughput observed at the end of one tuning period is less than 75% of the throughput seen at the end of the previous tuning period. The drop in throughput is not necessarily an indication of saturation. It may also be due to a reduction in offered load. My scheme treats both cases identically and decrements the estimate. If indeed the drop in throughput was due to a reduction in offered load, the reduced threshold will not harm performance as the threshold will be incremented gradually to the desired level when offered load increases.

- By what increments/decrements does Tune alter the estimate? Tune uses constant additive increments and decrements. Simulations with multiplicative

decrements show that constant additive tuning is adequate for effective self-tuning (See Section 3.4.3). For a reasonable range of values, (1% to 4% of all buffers) performance is insensitive (within 4%) to variations in increment/decrement values in a reasonable range of values and all values succeed in preventing performance degradation at saturation. The simulations showing the variation in Tune performance with different increment/decrement values are presented in Section 3.4.3. I use an increment of 1% of all buffers and a decrement of 4% of all buffers. For the network I consider, this corresponds to an increment of 30 and a decrement of 122.

To avoid local maxima, Tune resets the threshold to  $min(N_{max}, T_{max})$  when the throughput achieved in any single tuning period drops below 50% of the max value. It restarts max computation if the threshold is reset to  $min(N_{max}, T_{max})$  for r = 5 consecutive tuning periods.

To summarize the proposed implementation of Tune, it uses a sideband for communicating global congestion and throughput information. This mechanism provides delayed (32 cycles for the 16-ary, 2-cube) global snapshots of full buffer counts and throughput. Tune updates its threshold every 96 cycles in increments of 30 and decrements of 122. To avoid local maxima, Tune uses the scheme outlined in Section 3.2.2 with r = 5.

#### 3.2.2 Avoiding Local Maxima

To avoid settling at local maxima, Tune "remembers" the conditions that existed when maximum throughput was achieved. To do this, it keeps track of the maximum throughput (max) achieved during any single tuning period and remember the corresponding number of full buffers  $(N_{max})$  and threshold  $(T_{max})$ .

If the throughput in any tune-period drops significantly below the maximum

throughput, Tune tries to recreate the conditions that existed when maximum throughput was achieved. This is done by setting the threshold to  $min(T_{max}, N_{max})$ . If  $N_{max}$  is higher than  $T_{max}$ , it means that the network was throttling with a threshold value of  $T_{max}$  when it achieved the maximum observed throughput. In this case, the threshold is set to  $T_{max}$  so that the network can throttle new packets and drain existing packets till it reaches the desired load level. If, on the other hand,  $N_{max}$  is smaller than  $T_{max}$ , then setting the threshold to  $N_{max}$  is a better choice because it is possible that  $T_{max}$  is not low enough to prevent saturation. This guarantees that the tuning mechanism is not stuck at a local maximum after the network saturates.

It is possible that the threshold value which sustains high throughput for one communication pattern is not low enough to prevent saturation for another communication pattern. The *Tune* congestion control mechanism detects and adapts the threshold to such changes. If *Tune* resets the threshold to  $min(T_{max}, N_{max})$  for r consecutive tuning-periods, this means that even the  $min(T_{max}, N_{max})$  value is too high to prevent saturation, and *Tune* must recompute max value. In this case, max is reset to zero and the maximum locating process starts all over again. This ensures that the threshold adapts to changing communication patterns. I use r=5 for all experiments.

#### 3.2.3 Summary

The above discussion provides a general overview of a technique we believe can provide a robust, self-tuned congestion control. *Tune* gathers full-buffer counts and throughput measurements every 32 cycles. The full-buffer counts are used to estimate current congestion using linear extrapolation. This estimate is compared to a threshold to decide whether new packets are throttled. *Tune* uses a hill climbing algorithm to update its threshold every 96 cycles in increments and decrements of

1% and 4% of total buffer count, respectively. The hill climbing algorithm, when used alone, is susceptible to settling on local maxima after network saturation. Tune includes a mechanism to prevent this from happening by remembering maximum (max) observed throughput. Finally, Tune recomputes the maximum (max) if the threshold is reset for r = 5 consecutive tuning periods.

On a high level, Tune is somewhat analogous to TCP's self-tuning congestion control. Both have an idea of what the network performance should be. Expected round-trip time (RTT) in the case of TCP and max throughput in Tune's case. Both schemes allow offered load to incrementally increase as long as network performance is not penalized. The sliding window size increases as long as no packets are dropped in the case of TCP and threshold increases as long as there is no decrease in throughput in Tune. Both techniques take corrective action if network performance suffers. TCP reduces its window size and Tune either decrements the threshold or resets it to  $min(N_{max}, T_{max})$ . Finally, both schemes periodically refresh their estimate of network performance. TCP recomputes expected round-trip-time if packets are dropped, whereas Tune recomputes max,  $N_{max}$  and  $T_{max}$  if max is stale, i.e. if there are r consecutive corrective actions.

# 3.3 Methodology

To evaluate the *Tune* self-tuned congestion control scheme, I use the flexsim [60] simulator. I simulate a 16-ary, 2-cube (256 nodes) with full duplex physical links. Each node has one injection channel (through which packets sent by that node enter the network) and one delivery channel (through which packets sent to that node exit the network). I use three virtual channels per physical channel and edge-buffers (buffers associated with virtual channels) which can hold eight flits.

The router's arbiter is a central resource which only one packet can use at a time

and there's a one cycle routing delay per packet header. Packets obtain control of the router's arbiter on a demand-slotted round-robin distribution. This is not a bottleneck because routing occurs only for the header flit of a 16-flit packet. The remaining flits simply stream behind the header flit along the same switch path. It takes one cycle per flit to traverse the cross-bar switch and one cycle per flit to traverse a physical link.

I evaluate the *Tune* congestion control mechanism with both deadlock avoidance and deadlock recovery mechanisms. Deadlock avoidance uses the method proposed by Duato [18] with one escape virtual channel using oblivious dimension-order routing. I use the Disha [38] progressive deadlock recovery scheme with a time-out of 8 cycles.

All simulations execute for 60,000 cycles. However, I ignore the first 10,000 cycles to eliminate warm-up transients. Most results are presented in two parts: normalized delivered throughput (accepted flits/node/cycle) and average packet latency versus offered load in terms of packet injection rate.

The default load consists of each node generating 16 flit packets at the same fixed rate. I consider four different communication patterns, uniform random, bit-reversal, perfect-shuffle and complement. These communication patterns differ in the way a destination node is chosen for a given source node with bit co-ordinates  $(a_{n-1}, a_{n-2}, \ldots, a_1, a_0)$ . The bit co-ordinates for the destination nodes are  $(a_{n-2}, a_{n-3}, \ldots, a_0, a_{n-1})$  for perfect shuffle,  $(a_{n-1}, a_{n-2}, \ldots, a_1, a_0)$  for complement and  $(a_0, a_1, \ldots, a_{n-2}, a_{n-1})$  for bit-reversal.

I use synthetic workload, instead of full-blown multiprocessor workloads, for three reasons. First, my simulation environment cannot handle full-blown multiprocessor workloads. Second, my packet generation frequency corresponds to realistic miss rates in databases and scientific applications, which gives me confidence in the results. Third, the synthetic workloads nicely demonstrate the problem of network saturation

and avoids interactions with application-specific features.

For the network under consideration (with 3072 buffers), 12 bits are enough to count all buffers in the network. The network configuration needs 13 bits to represent the maximum possible aggregate throughput g \* NodeCount \* MaxTraffic = 32 \* 256 \* 1 = 8192 flits). Thus, *Tune* needs a total of 25 bits for the sideband signals. However, in Section 3.4.2, I demonstrate that it is possible to send these 25 bits using 9-bit sideband channels with very little performance degradation.

For comparison, I also simulate the At-Least-One (ALO) [4] congestion control scheme. ALO estimates global network congestion locally at each node. If at least one virtual channel is free on every useful <sup>1</sup> physical channel or if at least one useful physical channel has all its virtual channels free, then packet injection is allowed. Otherwise, new packets are throttled.

### 3.4 Simulation Results

The primary conclusions from my simulations are:

- Tune provides high performance consistently across different communication patterns and offered load levels.

- Tune outperforms an alternative congestion control technique that uses local estimates of congestion.

- Tune's self-tuning mechanism adapts the threshold dynamically to varying workloads and to bursty traffic.

The remainder of this section elaborates on each of these items.

<sup>&</sup>lt;sup>1</sup>useful is an output channel that can be used without violating the minimal-routing constraint.

#### 3.4.1 Overall Performance

I begin by examining the performance of a complete implementation, as described in Sections 3.1.1 and 3.2. Figure 3.4 shows the bandwidth and latency for a *uniform-random* traffic pattern for both deadlock recovery (a & b) and deadlock avoidance (c & d). Note the logarithmic scale used on the y-axis for the latency graphs (b & d).

The curve for the base case illustrates the network saturation problem. As load increases, the network throughput increases to a certain extent. However, at saturation, there is a sudden drop in throughput since only the escape channels are available to drain deadlocks. The configuration with deadlock recovery has lower bandwidth beyond saturation because Disha deadlock recovery requires that a packet obtain exclusive access to the deadlock-free path. In contrast, the deadlock avoidance scheme can break multiple deadlock cycles concurrently.